- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371341 > XC5215-3HQ208I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | XC5215-3HQ208I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門陣列(FPGA) |

| 文件頁(yè)數(shù): | 24/73頁(yè) |

| 文件大小: | 598K |

| 代理商: | XC5215-3HQ208I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)

R

XC5200 Series Field Programmable Gate Arrays

7-106

November 5, 1998 (Version 5.2)

Express Mode

Express mode is similar to Slave Serial mode, except the

data is presented in parallel format, and is clocked into the

target device a byte at a time rather than a bit at a time. The

data is loaded in parallel into eight different columns: it is

not internally serialized. Eight bits of configuration data are

loaded with every CCLK cycle, therefore this configuration

mode runs at eight times the data rate of the other six

modes. In this mode the XC5200 family is capable of sup-

porting a CCLK frequency of 10 MHz, which is equivalent to

an 80 MHz serial rate, because eight bits of configuration

data are being loaded per CCLK cycle. An XC5210 in the

Express mode, for instance, can be configured in about 2

ms. The Express mode does not support CRC error check-

ing, but does support constant-field error checking. A

length count is not used in Express mode.

In the Express configuration mode, an external signal

drives the CCLK input(s). The first byte of parallel configu-

ration data must be available at the D inputs of the FPGA

devices a short set-up time before the second rising CCLK

edge. Subsequent data bytes are clocked in on each con-

secutive rising CCLK edge. See

Figure 38 on page 123

.

Bitstream generation currently generates a bitstream suffi-

cient to program in all configuration modes except Express.

Extra CCLK cycles are necessary to complete the configu-

ration, since in this mode data is read at a rate of eight bits

per CCLK cycle instead of one bit per cycle. Normally the

entire start-up sequence requires a number of bits that is

equal to the number of CCLK cycles needed. An additional

five CCLKs (equivalent to 40 extra bits) will guarantee com-

pletion of configuration, regardless of the start-up options

chosen.

Multiple slave devices with identical configurations can be

wired with parallel D0-D7 inputs. In this way, multiple

devices can be configured simultaneously.

Pseudo Daisy Chain

Multiple devices with different configurations can be con-

nected together in a pseudo daisy chain, provided that all of

the devices are in Express mode. A single combined bit-

stream is used to configure the chain of Express mode

devices, but the input data bus must drive D0-D7 of each

device. Tie High the CS1 pin of the first device to be config-

ured, or leave it floating in the XC5200 since it has an inter-

nal pull-up. Connect the DOUT pin of each FPGA to the

CS1 pin of the next device in the chain. The D0-D7 inputs

are wired to each device in parallel. The DONE pins are

wired together, with one or more internal DONE pull-ups

activated. Alternatively, a 4.7 k

external resistor can be

used, if desired. (See

Figure 37 on page 122

.) CCLK pins

are tied together.

The requirement that all DONE pins in a daisy chain be

wired together applies only to Express mode, and only if all

devices in the chain are to become active simultaneously.

All devices in Express mode are synchronized to the DONE

pin. User I/O for each device become active after the

DONE pin for that device goes High. (The exact timing is

determined by options to the bitstream generation soft-

ware.) Since the DONE pin is open-drain and does not

drive a High value, tying the DONE pins of all devices

together prevents all devices in the chain from going High

until the last device in the chain has completed its configu-

ration cycle.

The status pin DOUT is pulled LOW two internal-oscillator

cycles (nominally 1 MHz) after INIT is recognized as High,

and remains Low until the device’s configuration memory is

full. Then DOUT is pulled High to signal the next device in

the chain to accept the configuration data on the D7-D0

bus. All devices receive and recognize the six bytes of pre-

amble and length count, irrespective of the level on CS1;

but subsequent frame data is accepted only when CS1 is

High and the device’s configuration memory is not already

full.

Setting CCLK Frequency

For Master modes, CCLK can be generated in one of three

frequencies. In the default slow mode, the frequency is

nominally 1 MHz. In fast CCLK mode, the frequency is

nominally 12 MHz. In medium CCLK mode, the frequency

is nominally 6 MHz. The frequency range is -50% to +50%.

The frequency is selected by an option when running the

bitstream generation software. If an XC5200-Series Master

is driving an XC3000- or XC2000-family slave, slow CCLK

mode must be used. Slow mode is the default.

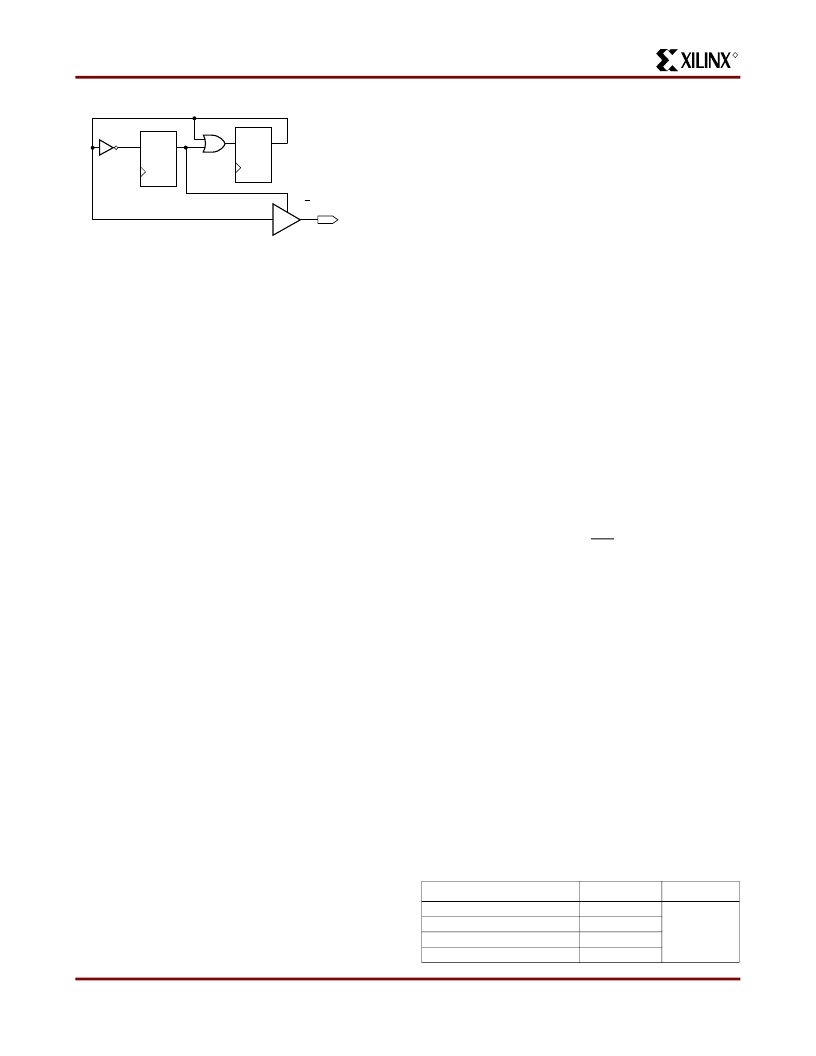

Output

Connected

to CCLK

OE/T

0

1

1

0

0

.

0

0

1

1

1

.

Reset

X5223

etc

Active Low Output

Active High Output

Figure 22: CCLK Generation for XC3000 Master

Driving an XC5200-Series Slave

Table 11: XC5200 Bitstream Format

Data Type

Value

Occurrences

Once per bit-

stream

Fill Byte

Preamble

Length Counter

Fill Byte

11111111

11110010

COUNT(23:0)

11111111

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5215-4HQ208I | Field Programmable Gate Array (FPGA) |

| XC5215-4HQ240I | Field Programmable Gate Array (FPGA) |

| XC5215-4PG299I | Field Programmable Gate Array (FPGA) |

| XC5215-4PQ160I | Field Programmable Gate Array (FPGA) |

| XC5215-5PG299I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5215-3HQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-3HQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-3HQ304C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-3HQ304I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-3PC84C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。