- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371341 > XC5215-3HQ208I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號: | XC5215-3HQ208I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數(shù): | 25/73頁 |

| 文件大?。?/td> | 598K |

| 代理商: | XC5215-3HQ208I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

November 5, 1998 (Version 5.2)

7-107

XC5200 Series Field Programmable Gate Arrays

7

Data Stream Format

The data stream (“bitstream”) format is identical for all con-

figuration modes, with the exception of Express mode. In

Express mode, the device becomes active when DONE

goes High, therefore no length count is required. Addition-

ally, CRC error checking is not supported in Express mode.

The data stream formats are shown in

Table 11

. Express

mode data is shown with D0 at the left and D7 at the right.

For all other modes, bit-serial data is read from left to right,

and byte-parallel data is effectively assembled from this

serial bitstream, with the first bit in each byte assigned to

D0.

The configuration data stream begins with a string of eight

ones, a preamble code, followed by a 24-bit length count

and a separator field of ones (or 24 fill bits, in Express

mode). This header is followed by the actual configuration

data in frames. The length and number of frames depends

on the device type (see

Table 12

). Each frame begins with

a start field and ends with an error check. In all modes

except Express mode, a postamble code is required to sig-

nal the end of data for a single device. In all cases, addi-

tional start-up bytes of data are required to provide four

clocks for the startup sequence at the end of configuration.

Long daisy chains require additional startup bytes to shift

the last data through the chain. All startup bytes are

don’t-cares; these bytes are not included in bitstreams cre-

ated by the Xilinx software.

In Express mode, only non-CRC error checking is sup-

ported. In all other modes, a selection of CRC or non-CRC

error checking is allowed by the bitstream generation soft-

ware. The non-CRC error checking tests for a designated

end-of-frame field for each frame. For CRC error checking,

the software calculates a running CRC and inserts a unique

four-bit partial check at the end of each frame. The 11-bit

CRC check of the last frame of an FPGA includes the last

seven data bits.

Detection of an error results in the suspension of data load-

ing and the pulling down of the INIT pin. In Master modes,

CCLK and address signals continue to operate externally.

The user must detect INIT and initialize a new configuration

by pulsing the PROGRAM pin Low or cycling Vcc.

Cyclic Redundancy Check (CRC) for

Configuration and Readback

The Cyclic Redundancy Check is a method of error detec-

tion in data transmission applications. Generally, the trans-

mitting system performs a calculation on the serial

bitstream. The result of this calculation is tagged onto the

data stream as additional check bits. The receiving system

performs an identical calculation on the bitstream and com-

pares the result with the received checksum.

Each data frame of the configuration bitstream has four

error bits at the end, as shown in

Table 11

. If a frame data

error is detected during the loading of the FPGA, the con-

figuration process with a potentially corrupted bitstream is

terminated. The FPGA pulls the INIT pin Low and goes into

a Wait state.

During Readback, 11 bits of the 16-bit checksum are added

to the end of the Readback data stream. The checksum is

computed using the CRC-16 CCITT polynomial, as shown

in

Figure 23

. The checksum consists of the 11 most signifi-

cant bits of the 16-bit code. A change in the checksum indi-

cates a change in the Readback bitstream. A comparison

to a previous checksum is meaningful only if the readback

data is independent of the current device state. CLB out-

puts should not be included (Read Capture option not

used). Statistically, one error out of 2048 might go undetec-

ted.

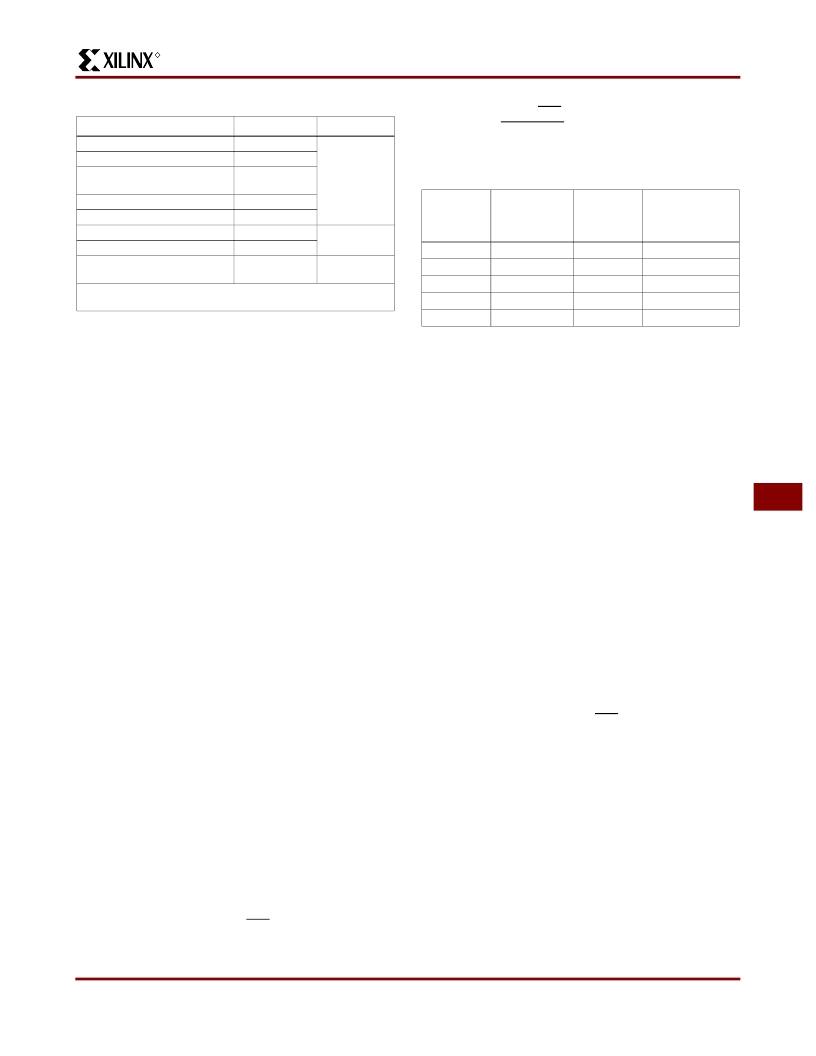

Start Byte

Data Frame *

Cyclic Redundancy Check or

Constant Field Check

Fill Nibble

Extend Write Cycle

Postamble

Fill Bytes (30)

Start-Up Byte

11111110

DATA(N-1:0)

CRC(3:0) or

0110

1111

FFFFFF

11111110

FFFF…FF

FF

Once per data

frame

Once per de-

vice

Once per bit-

stream

*Bits per Frame (N) depends on device size, as described for

table 11.

Table 11: XC5200 Bitstream Format

Data Type

Value

Occurrences

Table 12: Internal Configuration Data Structure

Device

VersaBlock

Array

PROM

Size

(bits)

42,416

70,704

106,288

165,488

237,744

Xilinx

Serial PROM

Needed

XC1765D

XC17128D

XC17128D

XC17256D

XC17256D

XC5202

XC5204

XC5206

XC5210

XC5215

Bits per Frame = (34 x number of Rows) + 28 for the top + 28 for

the bottom + 4 splitter bits + 8 start bits + 4 error check bits + 4 fill

bits

*

+ 24 extended write bits

= (34 x number of Rows) + 100

*

In the XC5202 (8 x 8), there are 8 fill bits per frame, not 4

Number of Frames = (12 x number of Columns) + 7 for the left

edge + 8 for the right edge + 1 splitter bit

= (12 x number of Columns) + 16

Program Data = (Bits per Frame x Number of Frames) + 48

header bits + 8 postamble bits + 240 fill bits + 8 start-up bits

= (Bits per Frame x Number of Frames) + 304

PROM Size = Program Data

8 x 8

10 x 12

14 x 14

18 x 18

22 x 22

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5215-4HQ208I | Field Programmable Gate Array (FPGA) |

| XC5215-4HQ240I | Field Programmable Gate Array (FPGA) |

| XC5215-4PG299I | Field Programmable Gate Array (FPGA) |

| XC5215-4PQ160I | Field Programmable Gate Array (FPGA) |

| XC5215-5PG299I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5215-3HQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-3HQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-3HQ304C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-3HQ304I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-3PC84C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。