- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19907 > XCF32PFSG48C (Xilinx Inc)IC PROM SRL 1.8V 32M 48CSBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XCF32PFSG48C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 13/35頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC PROM SRL 1.8V 32M 48CSBGA |

| 產(chǎn)品變化通告: | Package Assemble Change 01/Jan/2007 |

| 標(biāo)準(zhǔn)包裝: | 108 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 存儲(chǔ)容量: | 32Mb |

| 電源電壓: | 1.65 V ~ 2 V |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 48-BFBGA,CSPBGA |

| 供應(yīng)商設(shè)備封裝: | 48-CSP(8x9) |

| 包裝: | 托盤(pán) |

| 產(chǎn)品目錄頁(yè)面: | 601 (CN2011-ZH PDF) |

| 其它名稱: | 122-1457 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

Platform Flash In-System Programmable Configuration PROMs

DS123 (v2.18) May 19, 2010

Product Specification

20

R

THXT

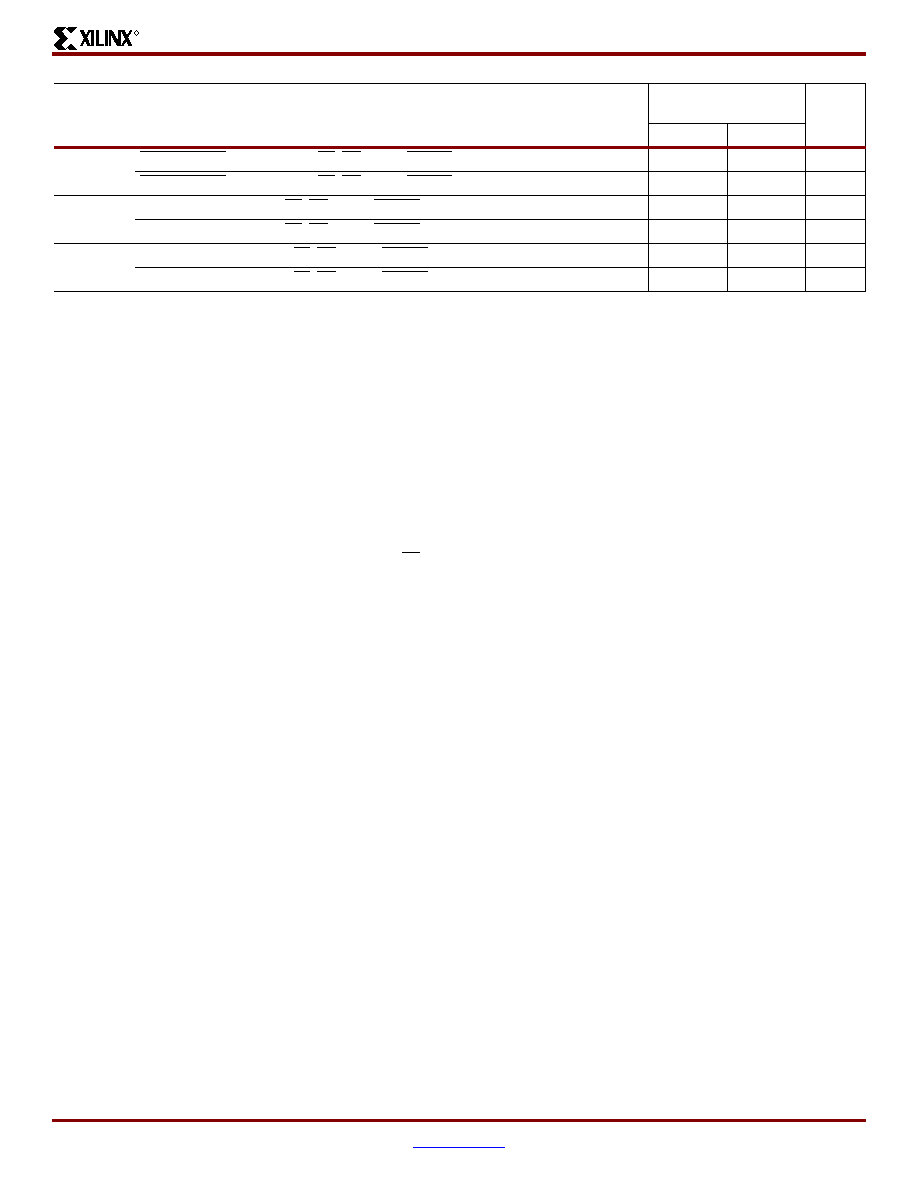

EN_EXT_SEL hold time from CF, CE, or OE/RESET when VCCO = 3.3V or 2.5V

300

–

ns

EN_EXT_SEL hold time from CF, CE, or OE/RESET when VCCO = 1.8V

300

–

ns

TSRV

REV_SEL setup time to CF, CE, or OE/RESET when VCCO = 3.3V or 2.5V

300

–

ns

REV_SEL setup time to CF, CE, or OE/RESET when VCCO = 1.8V

300

–

ns

THRV

REV_SEL hold time from CF, CE, or OE/RESET when VCCO = 3.3V or 2.5V

300

–

ns

REV_SEL hold time from CF, CE, or OE/RESET when VCCO = 1.8V

300

–

ns

Notes:

1.

AC test load = 50 pF for XCF01S/XCF02S/XCF04S; 30 pF for XCF08P/XCF16P/XCF32P.

2.

Float delays are measured with 5 pF AC loads.Transition is measured at ±200 mV from steady-state active levels.

3.

Guaranteed by design, not tested.

4.

All AC parameters are measured with VIL = 0.0V and VIH = 3.0V.

5.

If THCE High < 2 s, TCE = 2 s.

6.

If THOE Low < 2 s, TOE = 2 s.

7.

This is the minimum possible TCYCO. Actual TCYCO = TCCDD + FPGA Data setup time. Example: With the XCF32P in serial mode with VCCO

at 3.3V, if FPGA Data setup time = 15 ns, then the actual TCYCO = 25 ns +15 ns = 40 ns.

8.

The delay before the enabled CLKOUT signal begins clocking data out of the device is dependent on the clocking configuration. The delay

before CLKOUT is enabled increases if decompression is enabled.

9.

Slower CLK frequency option might be required to meet the FPGA data sheet setup time.

10. When decompression is enabled, the CLKOUT signal becomes a controlled clock output. When decompressed data is available, CLKOUT

toggles at the source clock frequency (either the selected internal clock frequency or the external CLK input frequency). When

decompressed data is not available, the CLKOUT pin is parked High. If CLKOUT is used, then it must be pulled High externally using a

4.7 k

Ω pull-up to V

CCO.

11. When JTAG CONFIG command is issued, PROM drives CF Low for at least the THCF minimum.

Symbol

Description

XCF08P, XCF16P,

XCF32P

Units

Min

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCF32PVOG48C | IC PROM SRL 1.8V 32M GATE 48TSOP |

| VI-24Y-CV | CONVERTER MOD DC/DC 3.3V 99W |

| RMC07DREN-S13 | CONN EDGECARD 14POS .100 EXTEND |

| VI-J2M-CY-B1 | CONVERTER MOD DC/DC 10V 50W |

| XC18V01PCG20C | IC PROM SERIAL CONFIG 1M 20-PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCF32PFSG48C4039 | 制造商:Xilinx 功能描述: |

| XCF32PFSG48C4118 | 制造商:Xilinx 功能描述: |

| XCF32PV | 制造商:XILINX 制造商全稱:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

| XCF32PV0G48C | 制造商:Xilinx 功能描述:PROM FLASH ISP 32M 1.8V 48TSOP 制造商:Xilinx 功能描述:PROM, FLASH ISP, 32M, 1.8V, 48TSOP 制造商:Xilinx 功能描述:IC FPGA CONFIG MEM 32MBIT 48-TSOP; Memory Type:Flash; Memory Size:32Mbit; Supply Voltage Min:1.65V; Supply Voltage Max:2V; Memory Case Style:TSOP; No. of Pins:48; IC Interface Type:JTAG, Parallel, Serial; Package / Case:48-TSOP ;RoHS Compliant: Yes |

| XCF32PVG | 制造商:XILINX 制造商全稱:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。