- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376454 > XR16L2750 (Exar Corporation) 2.25V TO 5.5V DUART WITH 64-BYTE FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | XR16L2750 |

| 廠商: | Exar Corporation |

| 英文描述: | 2.25V TO 5.5V DUART WITH 64-BYTE FIFO |

| 中文描述: | 2.25V至5.5V的杜阿爾特64字節(jié)FIFO |

| 文件頁數(shù): | 3/49頁 |

| 文件大小: | 602K |

| 代理商: | XR16L2750 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

XR16L2750

2.25V TO 5.5V DUART WITH 64-BYTE FIFO

REV. 1.0.0

á

3

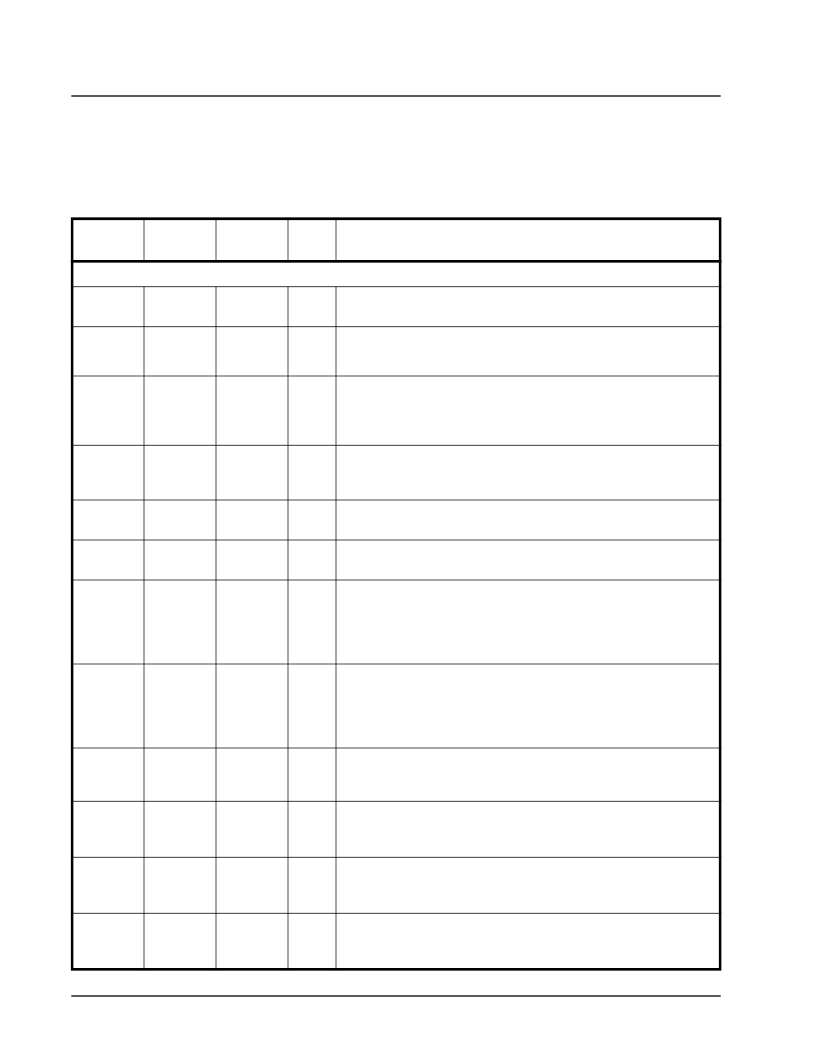

PIN DESCRIPTIONS

Pin Description

N

AME

44-PLCC

P

IN

#

48-TQFP

P

IN

#

T

YPE

D

ESCRIPTION

DATA BUS INTERFACE

A2:A0

29, 30, 31

26, 27, 28

I

Address data lines [2:0]. These 3 address lines select one of the inter-

nal registers in UART channel A/B during a data bus transaction.

D7:D0

9, 8, 7, 6, 5,

4, 3, 2

3, 2, 1, 48,

47, 46, 45,

44

19

I/O

Data bus lines [7:0] (bidirectional).

IOR#

24

I

Input/Output Read Strobe (active low). The falling edge instigates an

internal read cycle and retrieves the data byte from an internal register

pointed to by the address lines [A2:A0]. The data byte is placed on the

data bus to allow the host processor to read it on the rising edge.

IOW#

20

15

I

Input/Output Write Strobe (active low). The falling edge instigates an

internal write cycle and the rising edge transfers the data byte on the

data bus to an internal register pointed by the address lines.

CSA#

16

10

I

UART channel A select (active low) to enable UART channel A in the

device for data bus operation.

CSB#

17

11

I

UART channel B select (active low) to enable UART channel B in the

device for data bus operation.

INTA

33

30

O

UART channel A Interrupt output. The output state is defined by the

user through the software setting of MCR[3]. INTA is set to the active

mode and OP2A# output to a logic 0 when MCR[3] is set to a logic 1.

INTA is set to the three state mode and OP2A# to a logic 1 when

MCR[3] is set to a logic 0 (default). See MCR[3].

INTB

32

29

O

UART channel B Interrupt output. The output state is defined by the

user through the software setting of MCR[3]. INTB is set to the active

mode and OP2B# output to a logic 0 when MCR[3] is set to a logic 1.

INTB is set to the three state mode and OP2B# to a logic 1 when

MCR[3] is set to a logic 0 (default). See MCR[3].

TXRDYA#

1

43

O

UART channel A Transmitter Ready (active low). The output

provides the TX FIFO/THR status for transmit channel A. See

Table 2

. If it is not used, leave it unconnected.

RXRDYA#

34

31

O

UART channel A Receiver Ready (active low). This output provides the

RX FIFO/RHR status for receive channel A. See

Table 2

. If it is not

used, leave it unconnected.

TXRDYB#

12

6

O

UART channel B Transmitter Ready (active low). The output provides

the TX FIFO/THR status for transmit channel B. See

Table 2

. If it is not

used, leave it unconnected.

RXRDYB#

23

18

O

UART channel B Receiver Ready (active low). This output provides the

RX FIFO/RHR status for receive channel B. See

Table 2

. If it is not

used, leave it unconnected.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR16L2751 | 2.25V TO 5.5V DUART WITH 64-BYTE FIFO AND POWERSAVE |

| XR16L2751CM | 2.25V TO 5.5V DUART WITH 64-BYTE FIFO AND POWERSAVE |

| XR16L2751IM | 2.25V TO 5.5V DUART WITH 64-BYTE FIFO AND POWERSAVE |

| XR16L2752 | 2.25V TO 5.5V DUART WITH 64-BYTE FIFO |

| XR16L2752CJ | 2.25V TO 5.5V DUART WITH 64-BYTE FIFO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16L2750_05 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.25V TO 5.5V DUART WITH 64-BYTE FIFO |

| XR16L2750CJ | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.25V TO 5.5V DUART WITH 64-BYTE FIFO |

| XR16L2750CJ-0A-EB | 功能描述:UART 接口集成電路 Supports L2750 44 ld PLCC, ISA Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16L2750CJ-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16L2750CM | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.25V TO 5.5V DUART WITH 64-BYTE FIFO |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。