- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376459 > XRK4993IR-5 (EXAR CORP) 3.3V PROGRAMMABLE SKEW CLOCK BUFFER PDF資料下載

參數(shù)資料

| 型號: | XRK4993IR-5 |

| 廠商: | EXAR CORP |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 3.3V PROGRAMMABLE SKEW CLOCK BUFFER |

| 中文描述: | 4993 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | 0.150 INCH, QSOP-28 |

| 文件頁數(shù): | 9/13頁 |

| 文件大小: | 95K |

| 代理商: | XRK4993IR-5 |

XRK4993

9

REV. 1.0.0

3.3V PROGRAMMABLE SKEW CLOCK BUFFER

N

OTES

:

8.

Test measurement levels for the XRK4993 are TTL levels (1.5V to 1.5V). Test conditions assume signal transition

times of 2 ns or less and output loading as shown in the AC Test Loads and Waveforms unless otherwise

specified.

Guaranteed by statistical correlation. Tested initially and after any design or process changes that may affect

these parameters.

SKEW is defined as the time between the earliest and the latest output transition among all outputs for which the

same t

U

delay has been selected when all are loaded with 20pF and terminated with 75

Ω

to V

CC

/2 (XRK4993).

9.

10.

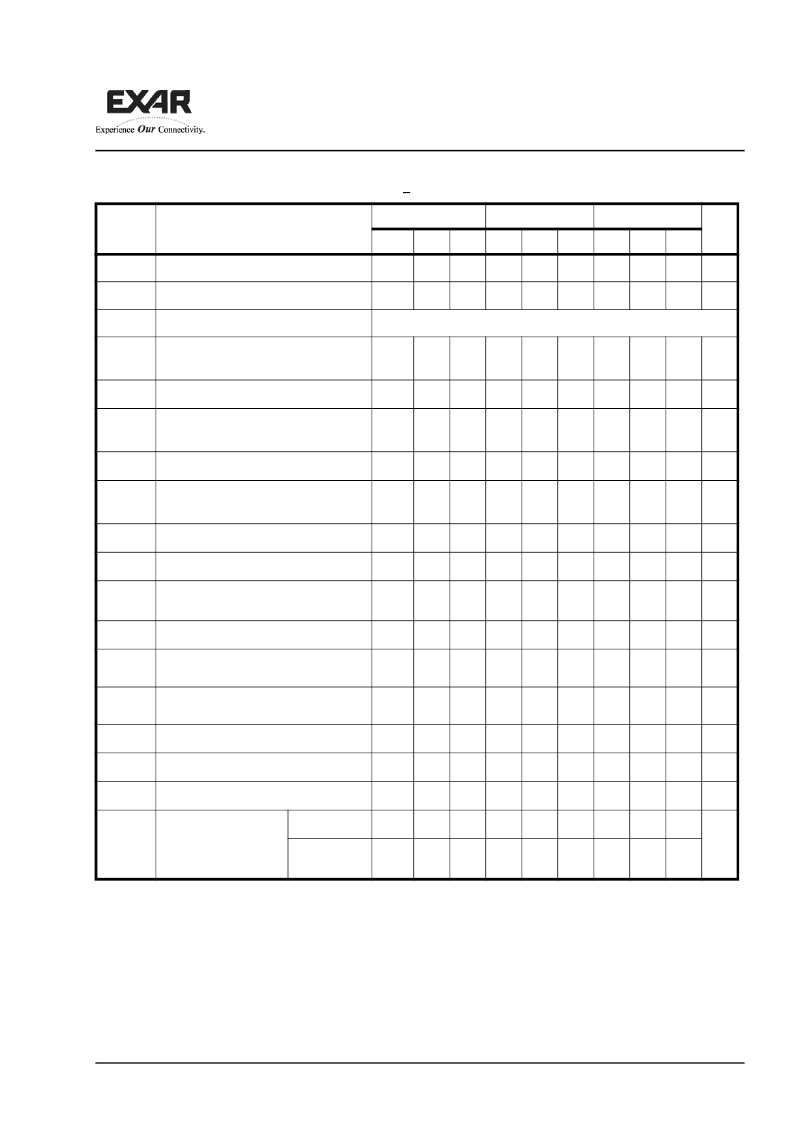

SWITCHING CHARACTERISTICS

OVER THE 3.3V + 10% OPERATING RANGE

[2,8]

S

YMBOL

D

ESCRIPTION

XRK4993-2

XRK4993-5

XRK4993-7

U

NIT

M

IN

T

YP

M

AX

M

IN

T

YP

M

AX

M

IN

T

YP

M

AX

t

RPWH

CLKIN Pulse Width HIGH

4

4

4

ns

t

RPWL

CLKIN Pulse Width LOW

4

4

4

ns

t

u

Programmable Skew Unit

See Table 1

t

SKEWPR

Zero Output Matched-Pair Skew

(Qx[1:0])

[10, 11]

0.05

0.2

0.1

0.25

0.1

0.25

ns

t

SKEW0

Zero Output Skew (All Outputs)

[10, 12]

0.1

0.25

0.25

0.5

0.3

0.75

ns

t

SKEW1

Output Skew (Rise-Rise, Fall-Fall,

Same Class Outputs)

[10, 13]

0.25

0.5

0.6

0.7

0.6

1

ns

t

SKEW2

Output Skew (Rise-Fall)

[10, 13]

0.3

1

0.5

1

1

1.5

ns

t

SKEW3

Output Skew (Rise-Rise, Fall-Fall,

Different Class Outputs)

[10, 13]

0.25

0.5

0.5

0.7

0.7

1.2

ns

t

SKEW4

Output Skew (Nominal-Divided)

[10, 13]

0.5

0.9

0.5

1

1.2

1.7

ns

t

DEV

Device-to-Device Skew

[9, 14]

0.75

1.25

1.65

ns

t

PD

Propagation Delay, CLKIN Rise to

FB_IN Rise

-0.25

0

0.25

-0.5

0

0.5

-0.7

0

0.7

ns

t

ODCV

Output Duty Cycle Variation

[15]

-1

0

1

-1

0

1

-1.2

0

1.2

ns

t

PWH

Output HIGH Time Deviation from 50%

[16]

2

2.5

3

ns

t

PWL

Output LOW Time Deviation from 50%

[16]

1.5

3

3.5

ns

t

ORISE

Output Rise Time

[16, 17]

0.15

1

1.2

0.15

1

1.5

0.15

1.5

2.5

ns

t

OFALL

Output Fall Time

[16, 17]

0.15

1

1.2

0.15

1

1.5

0.15

1.5

2.5

ns

t

LOCK

PLL Lock Time

[18]

0.5

0.5

0.5

ms

t

JR

Cycle-to-Cycle Output

Jitter

RMS

[9]

25

25

25

ps

Peak-to-Peak

[9]

200

200

200

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRK69772 | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69772CR | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69772IR | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69773 | 1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69773CR | 1:12 LVCMOS PLL CLOCK GENERATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRK4993IR-7 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PROGRAMMABLE SKEW CLOCK BUFFER |

| XRK69772 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69772CR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69772IR | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

| XRK69773 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1:12 LVCMOS PLL CLOCK GENERATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。