- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT8001 (Exar Corporation) WAN Clock for T1 and E1 Systems PDF資料下載

參數(shù)資料

| 型號: | XRT8001 |

| 廠商: | Exar Corporation |

| 英文描述: | WAN Clock for T1 and E1 Systems |

| 中文描述: | 廣域網(wǎng)時鐘T1和E1系統(tǒng) |

| 文件頁數(shù): | 32/48頁 |

| 文件大?。?/td> | 1054K |

| 代理商: | XRT8001 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

XRT8001

32

Rev. 1.01

1.544 MHz or

2.048 MHz

1.544 MHz or

2.048 MHz

CLK1

CLK2

6

13

8 kHz

F

IN

3

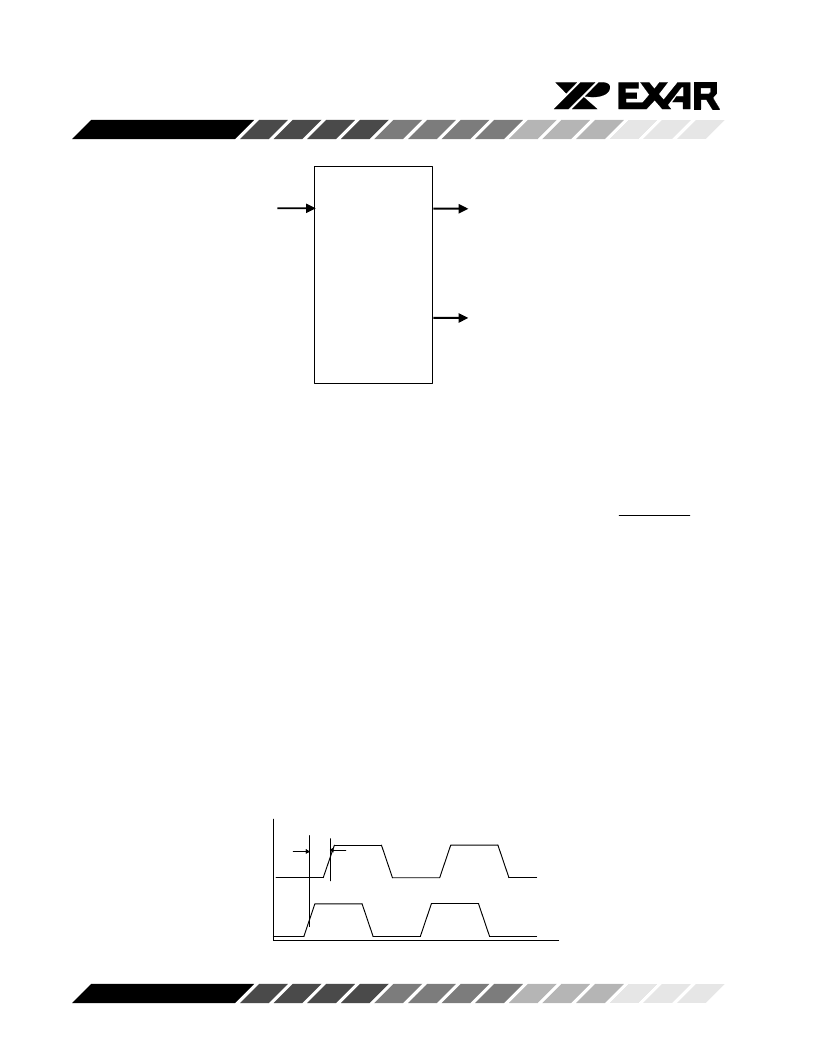

Figure 19. XRT8001 Reverse/Slave Mode

6.10 Phase relationship between the “FIN” input

and the “CLK1 and CLK2” outputs

The Phase relationship depends upon whether the

XRT8001 is operating in the “Slave” or “Master” Mode.

6.11 Slave Mode:

If the XRT8001 is operating in the “Slave” Mode, then

there is a specific phase relationship between the “FIN”

and the “CLK1, CLK2” outputs. The reasons are as

follows.

For Slave Mode Operation, the XRT8001 accepts a

8kHz clock signal (which it will also synthesize and

output via the SYNC output signal). Each of the two

PLLs (within the XRT8001) will be configured to gener-

ate either a “K x 56kHz” or a “K x 64kHz” clock signal.

Hence, in the “Slave Mode”, the “SYNC” output, is

simply a buffered version of the “FIN” input. Therefore,

generate a “K x 56kHz” clock signal.

the “SYNC” signal is approximately 4ns delayed from

the “FIN” input signal.

Each of the two PLLs “l(fā)ock” onto the “SYNC” signal, for

frequency synthesis.

This timing relationship (between FIN and the CLK1,

CLK2 signals) depends upon the “CLK1” and “CLK2”

signal frequencies and as listed in the following tables.

NOTES:

1.

Table 9 presents the timing relationship between the

“FIN” and the “CLK1, CLK2” if the PLLs are configured

generate a “K x 64kHz” clock signal.

2.

“FIN” and the “CLK1, CLK2” if the PLLs are configured to

generate a “K x 56kHz” clock signal.

Table 10 presents the timing relationship between the

FIN

CLK2

T

CLK1

or

Figure 20: Timing Relationship between the FIN and the “CLK1/CLK2” outputs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT8001ID | WAN Clock for T1 and E1 Systems |

| XRT8001IP | WAN Clock for T1 and E1 Systems |

| XRT8010 | 312MHZ CLOCK & CRYSTAL MULTIPLIER WITH LVDS OUTPUTS |

| XRT8010IL | 312MHZ CLOCK & CRYSTAL MULTIPLIER WITH LVDS OUTPUTS |

| XRT8020 | 650 MHZ CLOCK & CRYSTAL MULTIPLIER WITH LVDS OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT8001ES | 功能描述:鎖相環(huán) - PLL WAN CLOCK RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| XRT8001ID | 制造商:Exar Corporation 功能描述:WAN Clock 18-Pin SOIC W |

| XRT8001ID-F | 功能描述:鎖相環(huán) - PLL 3.3V-5V temp -45 to 85C RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| XRT8001ID-F | 制造商:Exar Corporation 功能描述:WAN Clock IC |

| XRT8001IDTR-F | 功能描述:鎖相環(huán) - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。