- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376464 > XRT91L30_0611 (Exar Corporation) STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號(hào): | XRT91L30_0611 |

| 廠商: | Exar Corporation |

| 英文描述: | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| 中文描述: | STS-12/STM-4或STS-3/STM-1的SONET / SDH收發(fā)器 |

| 文件頁(yè)數(shù): | 17/39頁(yè) |

| 文件大?。?/td> | 440K |

| 代理商: | XRT91L30_0611 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

xr

REV. 1.0.1

XRT91L30

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

15

2.3

The clock and data recovery (CDR) unit accepts the high speed NRZ serial data from the Differential LVPECL

receiver and generates a clock that is the same frequency as the incoming data. The clock recovery can either

utilize the transmitter’s CMU reference clock from either REFCLKP/N or TTLREFCLK or it can use

independent clock source CDRAUXREFCLK to train and monitor its clock recovery PLL. Initially upon startup,

the PLL locks to the local reference clock within ±500 ppm. Once this is achieved, the PLL then attempts to

lock onto the incoming receive data stream. Whenever the recovered clock frequency deviates from the local

reference clock frequency by more than approximately ±500 ppm, the clock recovery PLL will switch and lock

back onto the local reference clock. Whenever a Loss of Lock or a Loss of Signal event occurs, the CDR will

continue to supply a receive clock (based on the local reference) to the framer/mapper device. When the

LOSEXT is asserted by the optical module or when LOS is detected, the receive parallel data output will be

forced to a logic zero state for the entire duration that a LOS condition is detected. This acts as a receive data

mute upon LOS function to prevent random noise from being misinterpreted as valid incoming data. When the

LOSEXT becomes inactive and the recovered clock is determined to be within ±500 ppm accuracy with respect

to the local reference source and LOS is no longer declared, the clock recovery PLL will switch and lock back

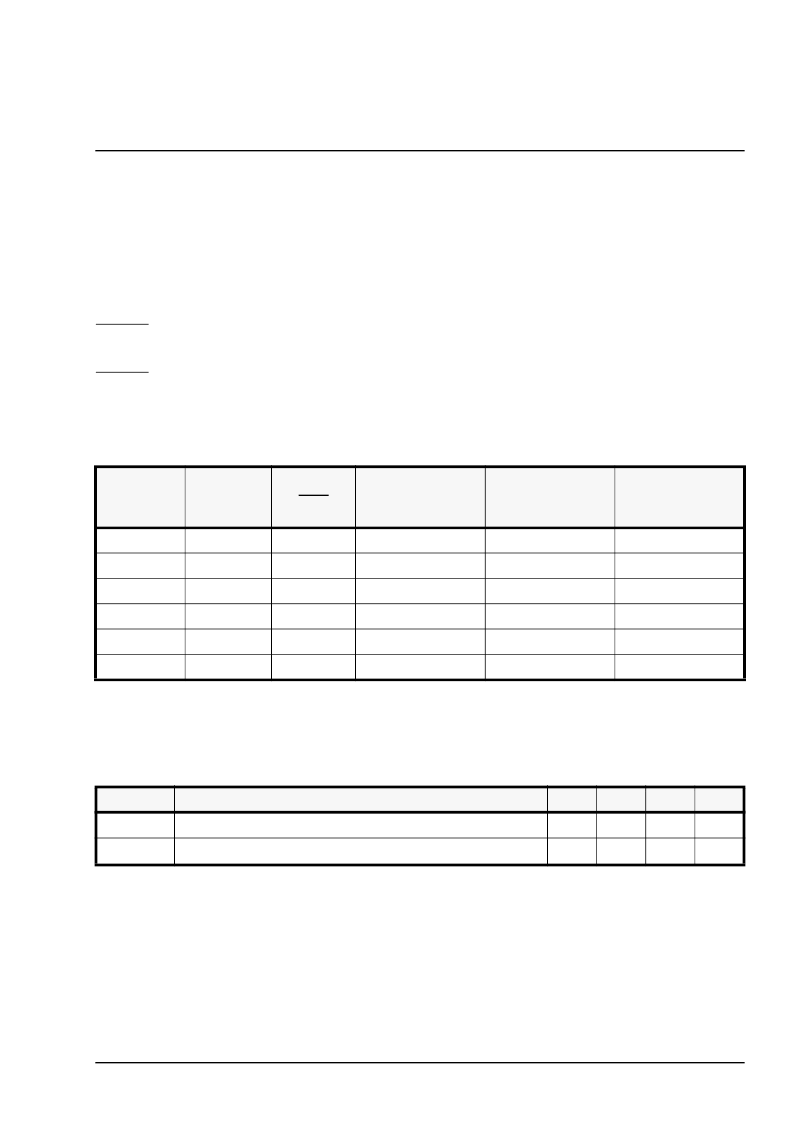

onto the incoming receive data stream. Table 5 shows Clock and Data Recovery reference clock settings.

Table 6 specifies the Clock and Data Recovery Unit performance characteristics.

T

ABLE

5: C

LOCK

D

ATA

R

ECOVERY

UNIT

REFERENCE

CLOCK

SETTINGS

Receive Clock and Data Recovery

1

Requires frequency accuracy better than 20ppm in order for the transmitted data rate frequency to have the necessary

accuracy required for SONET systems.

2

CDRAUXREFCLK requires accuracy of 77.76 MHz +/- 200ppm.

T

ABLE

6: C

LOCK

AND

D

ATA

R

ECOVERY

U

NIT

P

ERFORMANCE

CMUFREQSEL CDRREFSEL

STS12/

STS3

REFCLKP/N

1OR

TTLREFCLK

1

F

REQUENCY

(MH

Z

)

CDRAUXREFCLK

2

F

REQUENCY

(MH

Z

)

CDR O

UTPUT

F

REQUENCY

(MH

Z

)

0

0

0

77.76 MHz

not used

155.52

0

0

1

77.76 MHz

not used

622.08

1

0

0

19.44 MHz

not used

155.52

1

0

1

19.44 MHz

not used

622.08

X

1

0

not referenced by CDR

77.76 MHz

155.52

X

1

1

not referenced by CDR

77.76 MHz

622.08

N

AME

P

ARAMETER

M

IN

T

YP

M

AX

U

NITS

REF

DUTY

Reference clock duty cycle

40

60

%

REF

TOL

Reference clock frequency tolerance

-200

+200

ppm

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L306 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30IQ | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L31 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L31IQ | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L306 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30ES | 功能描述:總線(xiàn)收發(fā)器 RoHS:否 制造商:Fairchild Semiconductor 邏輯類(lèi)型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類(lèi)型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L30IQ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT91L30IQ-F | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 8-Bit TTL 3.3V temp -45 to 85C;UART RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT91L30IQ-F | 制造商:Exar Corporation 功能描述:SONET Transceiver IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。