- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376464 > XRT91L32 (Exar Corporation) STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號(hào): | XRT91L32 |

| 廠商: | Exar Corporation |

| 英文描述: | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| 中文描述: | STS-12/STM-4或STS-3/STM-1的SONET / SDH收發(fā)器 |

| 文件頁數(shù): | 11/37頁 |

| 文件大小: | 417K |

| 代理商: | XRT91L32 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

xr

REV. 1.0.2

XRT91L32

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

9

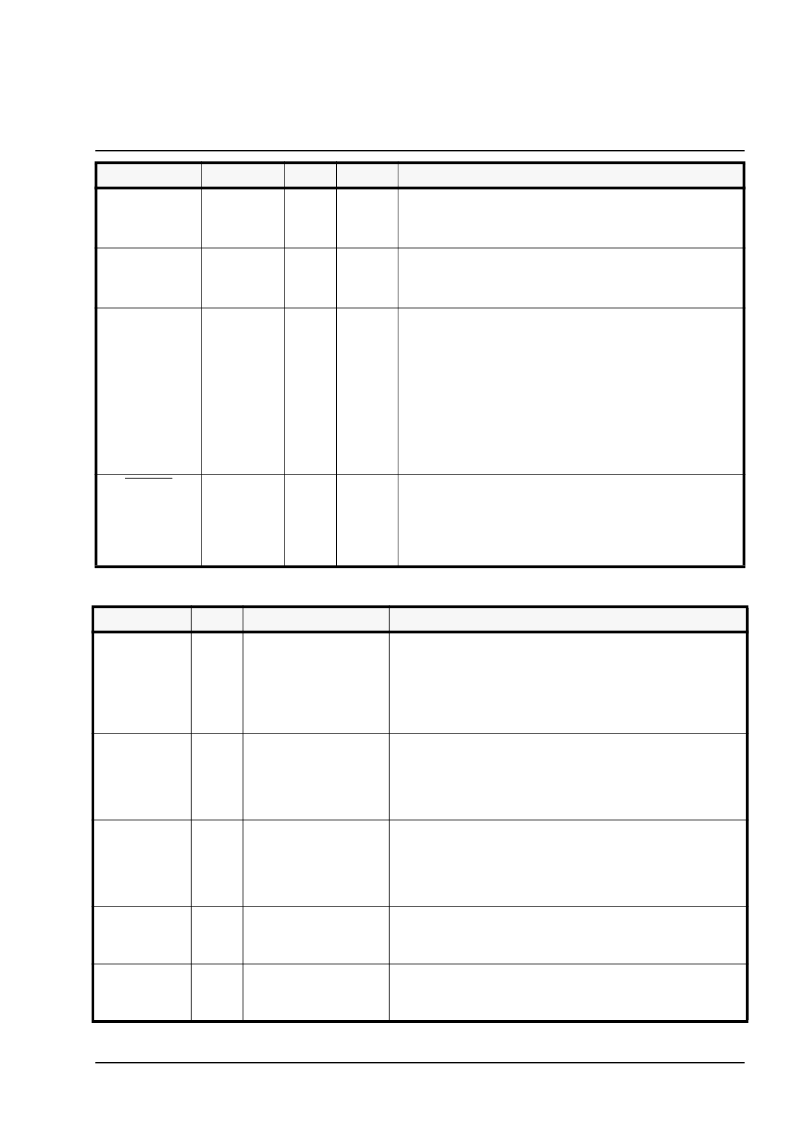

POWER AND GROUND

CAP1P

CAP2P

Analog

-

63

66

CDR Non-Inverting External Feeback Capacitor

C1 = 0.47

μ

F ± 10% tolerance

(Isolate from noise and place close to pin)

CAP1N

CAP2N

Analog

-

64

65

CDR Inverting External Feeback Capacitor

C2 = 0.47

μ

F ± 10% tolerance

(Isolate from noise and place close to pin)

DLOSDIS

LVTTL

I

17

LOS (Los of Signal) Detect Disable

Disables internal LOS monitoring and automatic muting of

RXDO[7:0] upon LOS detection (according to gating shown in

Figure 7.) LOS is declared when

a string of 128 consecutive

zeros occur on the line. LOS condition is cleared when the 16

or more pulse transitions is detected for 128 bit period sliding

window.

"Low" = Monitor and Mute received data upon LOS declaration

"High" = Disable internal LOS monitoring (see Figure 7 for logic

operation.)

LOSEXT

SE-LVPECL

I

53

LOS or Signal Detect Input from Optical Module

Active "Low." When active, this pin can force the received data

output bus RXDO[7:0] to a logic state of ’0’ per Figure 7.

"Low" = Forced LOS

"High" = Normal Operation

N

AME

T

YPE

P

IN

D

ESCRIPTION

VDD3.3

PWR

2,28,31,49,54,58,76,99

3.3V CMOS Power Supply

VDD3.3 should be isolated from the analog VDD power supplies.

Use a ferrite bead along with an internal power plane separation.

The VDD3.3 power supply pins should have bypass capacitors to

the nearest ground. For best results, refer to Application notes

about general board layout guidelines.

AVDD3.3_TX

PWR

62

Analog 3.3V Transmitter Power Supply

AVDD3.3_TX should be isolated from the digital power supplies.

For best results, use a ferrite bead along with an internal power

plane separation. The AVDD3.3_TX power supply pins should

have bypass capacitors to the nearest ground.

AVDD3.3_RX

PWR

67,,68,69

Analog 3.3V Receiver Power Supply

AVDD3.3_RX should be isolated from the digital power supplies.

For best results, use a ferrite bead along with an internal power

plane separation. The AVDD3.3_RX power supply pins should

have bypass capacitors to the nearest ground.

VDD_LVPECL

PWR

9,15,21

3.3V Input/Output LVPECL Bus Power Supply

These pins require a 3.3V potential voltage for properly biasing

the Differential LVPECL input and output pins.

AGND_TX

PWR

59,60

Transmitter Analog Ground for 3.3V Analog Power Supplies

It is recommended that all ground pins of this device be tied

together.

N

AME

L

EVEL

T

YPE

P

IN

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L32IQ-F | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L80 | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L80_0507 | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L80IB | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L81 | 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L32ES | 功能描述:LIN 收發(fā)器 SONET SDH 8 bit TRANCEIVER RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L32IQ | 功能描述:LIN 收發(fā)器 SONET SDH 8 bit TRANCEIVER RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L32IQ-F | 功能描述:總線收發(fā)器 8-Bit TTL 3.3V temp -45 to 85C;UART RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L32IQTR | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L32IQTR-F | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。