- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376464 > XRT91L32 (Exar Corporation) STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號(hào): | XRT91L32 |

| 廠商: | Exar Corporation |

| 英文描述: | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| 中文描述: | STS-12/STM-4或STS-3/STM-1的SONET / SDH收發(fā)器 |

| 文件頁數(shù): | 26/37頁 |

| 文件大小: | 417K |

| 代理商: | XRT91L32 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

XRT91L32

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

xr

REV. 1.0.2

24

Jitter specification is defined using a 12kHz to 1.3/5MHz LP-HP single-pole filter.

1

These reference clock jitter limits are required for the outputs to meet SONET system level jitter requirements (<10 mUI

rms

).

2

Required to meet SONET output frequency stability requirements.

3.5

Two types of loop timing are possible in the XRT91L32.

In the internal loop timing mode, loop timing is controlled by the LOOPTIME pin. This mode is selected by

asserting the LOOPTIME signal to a high level. When the loop timing mode is activated, the CMU synthesized

hi-speed reference clock input to the Retimer is replaced with the hi-speed internally recovered receive clock

coming from the CDR. Under this condition both the transmit and receive sections are synchronized to the

internally recovered receive clock. Loop time mode directly locks the Retimer to the recovered receive clock.

In external loop timing mode, the XRT91L32 allows the user the flexibility of using an externally recovered

receive clock for retiming the high speed serial data. First, the CDRDIS input pin should be set high. By doing

so, the internal CDR is disabled and bypassed and the XRT91L32 will sample the incoming high speed serial

data on RXIP/N with the externally recovered receive clock connected to the XRXCLKIP/N inputs. In this state,

the receive clock de-jittering and recovery is done externally and fed thru XRXCLKIP/N and the XRT91L32 will

sample RXIP/N on the rising edge of XRXCLKIP/N. Secondly, the LOOPTIME pin must also be set high in

order to select the externally recovered receive clock on XRXCLKIP/N as the reference clock source for the

transmit serial data output stream TXOP/N.

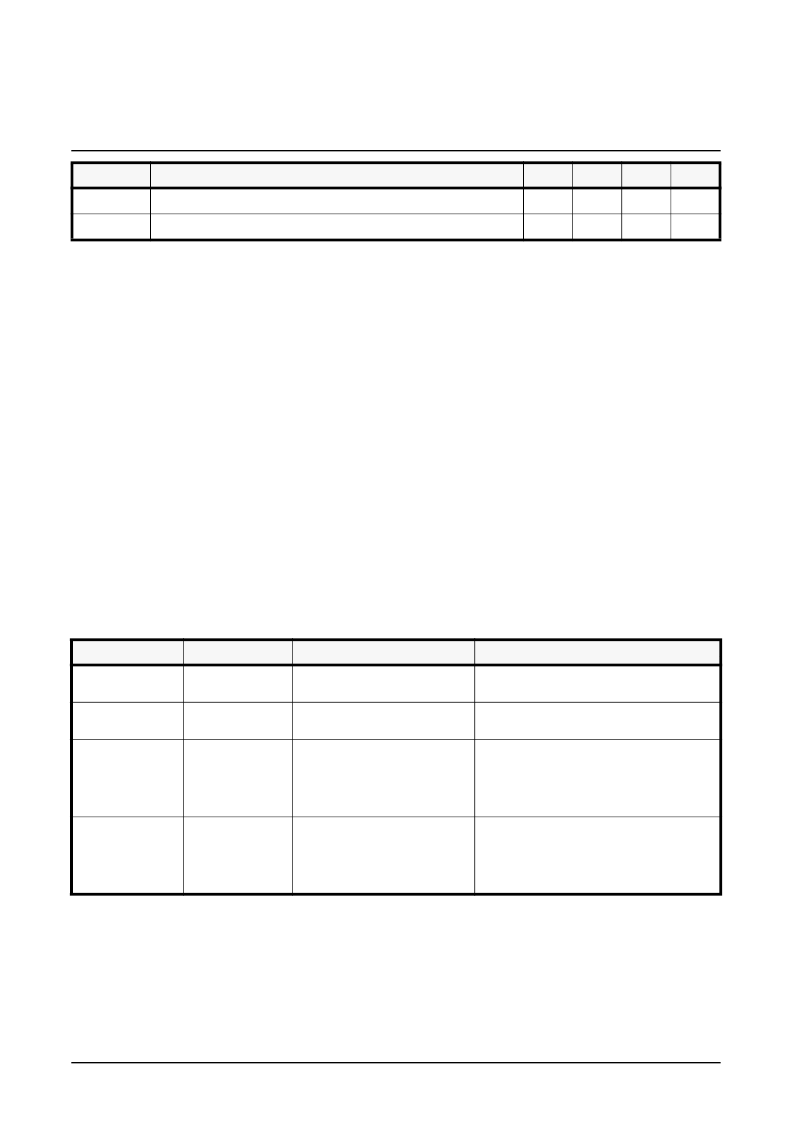

Table 13 provides configuration for selecting the loop timing and clock recovery modes. The use of the on-chip

CDR or an external recovered clock in loop timing applications is shown in Figure 14.

Loop Timing and Clock Control

OCLK

FREQ

Frequency output

620

624

MHz

OCYC

DUTY

Clock output duty cycle (’1010’ data pattern)

45

55

%

T

ABLE

13: L

OOP

T

IMING

AND

C

LOCK

R

ECOVERY

CONFIGURATIONS

CDRDIS

LOOPTIME

T

RANSMIT

C

LOCK

S

OURCE

R

ECEIVE

C

LOCK

S

OURCE

0

0

Clock Multiplier Unit

CDR Enabled.

Clock and Data recovery by internal CDR

0

1

Internal CDR

CDR Enabled.

Clock and Data recovery by internal CDR

1

0

Clock Multiplier Unit

CDR Disabled.

Externally recovered Receive Clock from

XRXCLKIP/N

622.08/155.52 Mbps data on RXIP/N sampled at

rising edge of XRXCLKIP/N

1

1

External CDR thru XRXCLKIP/N

CDR Disabled.

Externally recovered Receive Clock from

XRXCLKIP/N

622.08/155.52 Mbps data on RXIP/N sampled at

rising edge of XRXCLKIP/N

N

AME

P

ARAMETER

M

IN

T

YP

M

AX

U

NITS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L32IQ-F | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L80 | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L80_0507 | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L80IB | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L81 | 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L32ES | 功能描述:LIN 收發(fā)器 SONET SDH 8 bit TRANCEIVER RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L32IQ | 功能描述:LIN 收發(fā)器 SONET SDH 8 bit TRANCEIVER RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L32IQ-F | 功能描述:總線收發(fā)器 8-Bit TTL 3.3V temp -45 to 85C;UART RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L32IQTR | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L32IQTR-F | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。