- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373771 > Z8S18020VSC (ZILOG INC) 8 PIN,STRAIGHTTHRU FUTUREBUS POWER PDF資料下載

參數(shù)資料

| 型號(hào): | Z8S18020VSC |

| 廠商: | ZILOG INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8 PIN,STRAIGHTTHRU FUTUREBUS POWER |

| 中文描述: | 8-BIT, MICROPROCESSOR, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁(yè)數(shù): | 62/70頁(yè) |

| 文件大小: | 387K |

| 代理商: | Z8S18020VSC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)當(dāng)前第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)

Z80180/Z8S180/Z8L180

Enhanced Z180 Microprocessor

Zilog

1-62

P R E L I M I N A R Y

DS971800401

Refresh Control and Reset.

After RESET, based on the

initialized value of RCR, refresh cycles will occur with an

interval of 10 clock cycles and be 3 clock cycles in dura-

tion.

Dynamic RAM Refresh Operation

1.

Refresh Cycle insertion is stopped when the CPU is in

the following states:

a.

During RESET

b.

When the bus is released in response to

BUSREQ.

c.

During SLEEP mode.

d.

During WAIT states.

2.

Refresh cycles are suppressed when the bus is

released in response to BUSREQ. However, the

refresh timer continues to operate. Thus, the time at

which the first refresh cycle occurs after the

Z80180/Z8S180/Z8L180 re-acquires the bus depends

on the refresh timer and has no timing relationship with

the bus exchange.

3.

Refresh cycles are suppressed during SLEEP mode.

If a refresh cycle is requested during SLEEP mode,

the refresh cycle request is internally “l(fā)atched” (until

replaced with the next refresh request). The “l(fā)atched”

refresh cycle is inserted at the end of the first machine

cycle after SLEEP mode is exited. After this initial

cycle, the time at which the next refresh cycle occurs

depends on the refresh time and has no relationship

with the exit from SLEEP mode.

4.

The refresh address is incremented by one for each

successful refresh cycle, not for each refresh. Thus,

independent of the number of “missed” refresh

requests, each refresh bus cycle will use a refresh

address incremented by one from that of the previous

refresh bus cycles.

MMU COMMON BASE REGISTER

Mnemonic CBR

Address 38

MMU Common Base Register (CBR).

CBR specifies the

base address (on 4 KB boundaries) used to generate a 20-

bit physical address for Common Area 1 accesses. All bits

of CBR are reset to 0 during RESET.

Table 14. DRAM Refresh Intervals

Insertion

Interval

10 states

20 states

40 states

80 states

Time Interval

6 MHz

1.66

μ

s

3.3

μ

s

6.6

μ

s

13.3

μ

s

CYC1

0

0

1

1

CYC0

0

1

0

1

: 10 MHz

(1.0

μ

s)*

(2.0

μ

s)*

(4.0

μ

s)*

(8.0

μ

s)*

8 MHz

(1.25

μ

s)*

(2.5

μ

s)*

(5.0

μ

s)*

(10.0

μ

s)*

4 MHz

2.5

μ

s

5.0

μ

s

10.0

μ

s

20.0

μ

s

2.5 MHz

4.0

μ

s

8.0

μ

s

16.0

μ

s

32.0

μ

s

Note:

*calculated interval

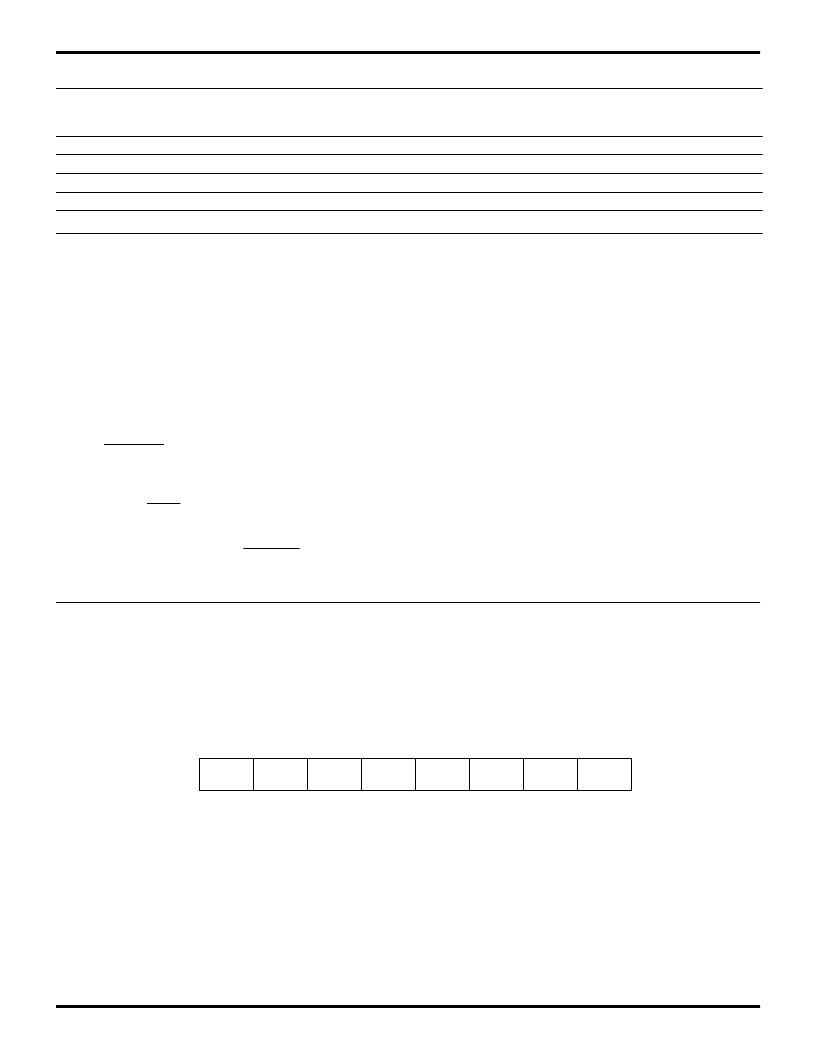

Figure 79. MMU Common Base Register (BBR: I/O Address = 38H)

Bit

CB7

CB6

R/W

CB5

7

6

5

4

3

2

1

0

CB4

CB2

CB1

CB0

R/W

CB3

R/W

R/W

R/W

R/W

R/W

R/W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z8S18033FEC | ENHANCED Z180 MICROPROCESSOR |

| Z8S18033FSC | CONN POWER HEADER 5ROW 10POS P-F |

| Z8S18033PEC | ENHANCED Z180 MICROPROCESSOR |

| Z8S18033PSC | ENHANCED Z180 MICROPROCESSOR |

| Z8S18033VEC | CONN HDR INVERSE 30POS 5ROW R/A |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z8S18020VSC00TR | 功能描述:IC Z180 MPU 68PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Z180 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| Z8S18020VSC1960 | 功能描述:微處理器 - MPU 20MHz STATIC Z180 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| Z8S18020VSC1960TR | 功能描述:IC Z180 MPU 68PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Z180 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| Z8S18020VSG | 功能描述:微處理器 - MPU 20MHz STATIC Z180 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| Z8S18020VSG00TR | 制造商:Zilog Inc 功能描述:Z8S180 Series 20 MHz 5 V Surface Mount Enhanced Z180 Microprocessor - PLCC-68 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。