- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371396 > 24AA512 (Microchip Technology Inc.) 512K I2C CMOS Serial EEPROM PDF資料下載

參數(shù)資料

| 型號: | 24AA512 |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | 512K I2C CMOS Serial EEPROM |

| 中文描述: | 為512k的I2C的CMOS串行EEPROM |

| 文件頁數(shù): | 5/26頁 |

| 文件大?。?/td> | 420K |

| 代理商: | 24AA512 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

2004 Microchip Technology Inc.

DS21754E-page 5

24AA512/24LC512/24FC512

2.0

PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

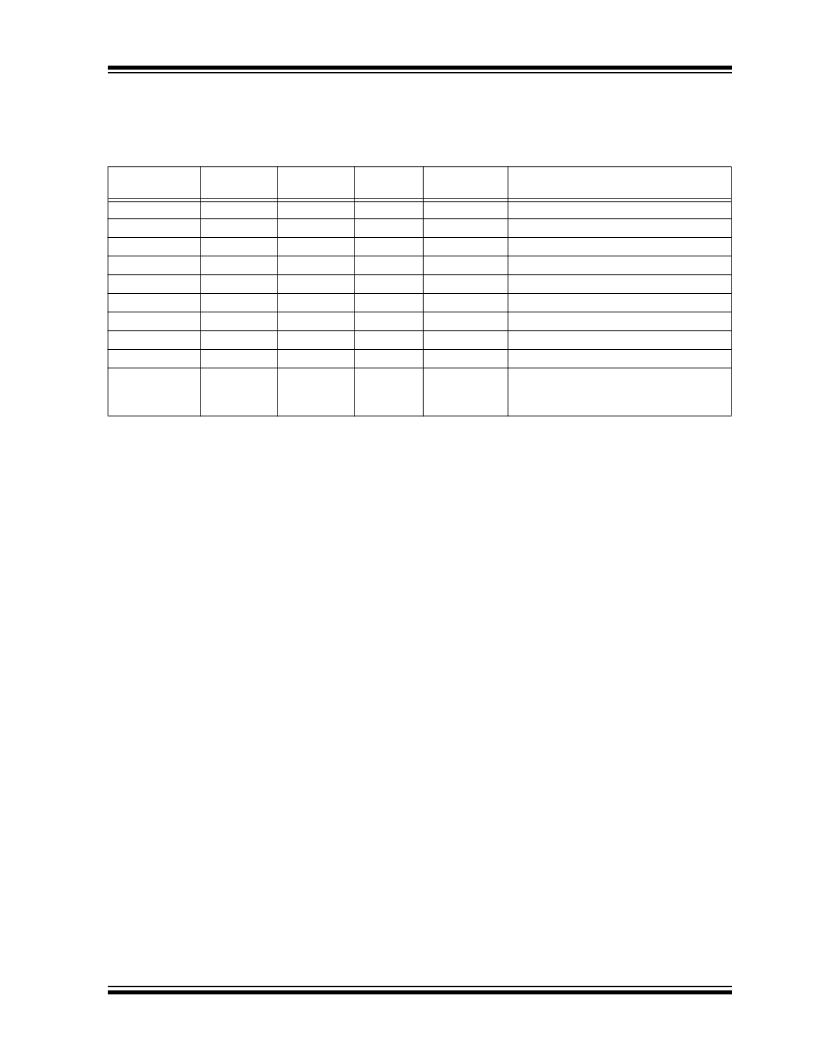

TABLE 2-1:

PIN FUNCTION TABLE

2.1

A0, A1 and A2 Chip Address

Inputs

The A0, A1 and A2 inputs are used by the 24XX512 for

multiple device operations. The logic levels on these

inputs are compared with the corresponding bits in the

slave address. The chip is selected if the compare is

true.

Up to eight devices may be connected to the same bus

by using different Chip Select bit combinations. If these

pins are left unconnected, the inputs will be pulled

down internally to V

SS

. If they are tied to V

CC

or driven

high, the internal pull-down circuitry is disabled.

In most applications, the chip address inputs A0, A1,

and A2 are hard-wired to logic ‘

0

’ or logic ‘

1

’. For

applications in which these pins are controlled by a

microcontroller or other programmable logic device,

the chip address pins must be driven to logic ‘

0

’ or logic

‘

1

’ before normal device operation can proceed.

2.2

Serial Data (SDA)

This is a bidirectional pin used to transfer addresses

and data into and data out of the device. It is an open-

drain terminal, therefore, the SDA bus requires a pull-

up resistor to V

CC

(typical 10 k

for 100 kHz, 2 k

for

400 kHz and 1 MHz).

For normal data transfer, SDA is allowed to change

only during SCL low. Changes during SCL high are

reserved for indicating the Start and Stop conditions.

2.3

Serial Clock (SCL)

This input is used to synchronize the data transfer from

and to the device.

2.4

Write-Protect (WP)

This pin can be connected to either V

SS

or V

CC

.

Internal pull-down circuitry on this pin will keep the

device in the unprotected state if left floating, however,

floating this pin is not recommended for most

applications. If tied to V

SS

, normal memory operation is

enabled (read/write the entire memory 0000-FFFF).

If tied to V

CC

, write operations are inhibited. Read

operations are not affected.

3.0

FUNCTIONAL DESCRIPTION

The 24XX512 supports a bidirectional 2-wire bus and

data transmission protocol. A device that sends data

onto the bus is defined as a transmitter and a device

receiving data as a receiver. The bus must be

controlled by a master device which generates the

serial clock (SCL), controls the bus access and

generates the Start and Stop conditions, while the

24XX512 works as a slave. Both master and slave

can operate as a transmitter or receiver, but the

master device determines which mode is activated.

Name

PDIP

SOIC

14-lead

TSSOP

1

2

3, 4, 5

6

7

8

9

10, 11, 12

13

14

DFN

Function

A0

A1

(NC)

A2

V

SS

SDA

SCL

(NC)

WP

V

CC

1

2

—

3

4

5

6

—

7

8

1

2

—

3

4

5

6

—

7

8

1

2

—

3

4

5

6

—

7

8

User Configured Chip Select

User Configured Chip Select

Not Connected

User Configured Chip Select

Ground

Serial Data

Serial Clock

Not Connected

Write-Protect Input

+1.8V to 5.5V (24AA512)

+2.5V to 5.5V (24LC512)

+2.5V to 5.5V (24FC512)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC512 | 512K I2C CMOS Serial EEPROM |

| 24FC515 | 512K I2C CMOS Serial EEPROM |

| 24AA515 | 512K I2C CMOS Serial EEPROM |

| 24LC515 | 512K I2C CMOS Serial EEPROM |

| 24FC65-IP | 64K 5.0V 1 MHz I 2 C Smart Serial EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24AA512/S16K | 制造商:Microchip Technology Inc 功能描述:512K, 64K X 8, 1.8V SER EE,DIE - Gel-pak, waffle pack, wafer, diced wafer on film |

| 24AA512/W16K | 制造商:Microchip Technology Inc 功能描述:512K, 64K X 8, 1.8V SER EE,WAFER - Gel-pak, waffle pack, wafer, diced wafer on film |

| 24AA512/WF16K | 制造商:Microchip Technology Inc 功能描述:512K, 64K X 8, 1.8V SER EE,WAF - Gel-pak, waffle pack, wafer, diced wafer on film |

| 24AA512-I/MF | 功能描述:電可擦除可編程只讀存儲器 64kx8 - 1.8V RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| 24AA512-I/MS | 制造商:Microchip Technology Inc 功能描述:512K, 64K X 8, 1.8V SER EE, IND - Rail/Tube 制造商:Microchip Technology Inc 功能描述:IC EEPROM 512KBIT 400KHZ 8MSOP 制造商:Microchip Technology Inc 功能描述:512K, 64K X 8, 1.8V SER EE, IND, 8 MSOP 3x3mm TUBE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。