- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄33600 > 405EX (Applied Micro Circuits Corp.) PowerPC 405EX Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | 405EX |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | PowerPC 405EX Embedded Processor |

| 中文描述: | 嵌入式處理器的PowerPC 405EX |

| 文件頁數(shù): | 31/67頁 |

| 文件大?。?/td> | 457K |

| 代理商: | 405EX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

PPC405EX – PowerPC 405EX Embedded Processor

Revision 1.09 - August 21, 2007

AMCC Proprietary

37

Preliminary Data Sheet

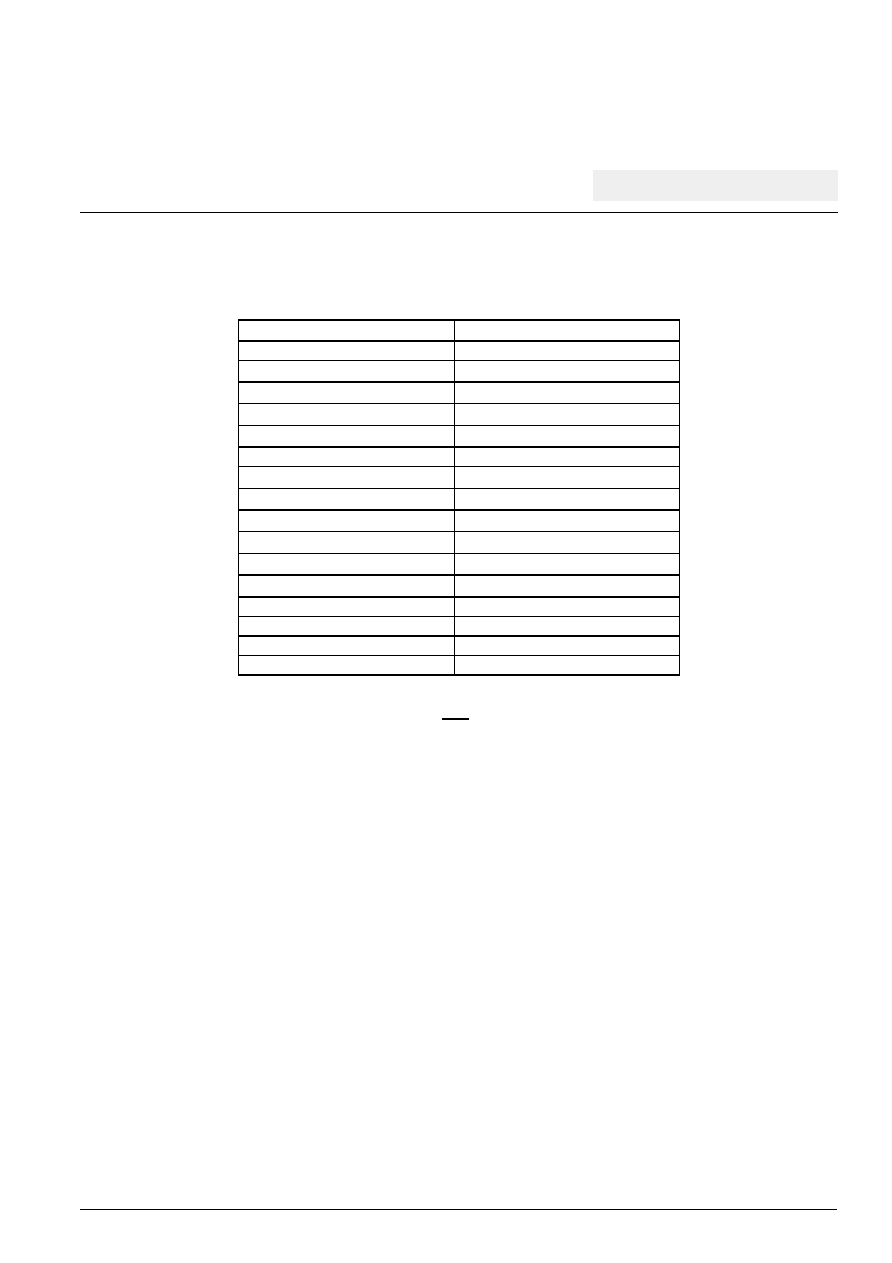

Pin Group List

The following table provides a summary of the number of package pins (balls) associated with each functional

interface group.

In the table “Signal Functional Description” on page 38, each external signal is listed along with a short description

of the signal function. Active-low signals (for example, Halt) are marked with an overline. See the preceding table,

“Signals Listed Alphabetically” on page 17, for the pin (ball) number to which each signal is assigned.

Shared Pins

Some signals are shared on the same package pin so that the pin can be used for different functions. In most

cases, the signal names shown in this table are not accompanied by signal names that might share the same pin.

If you need to know what, if any, signals are shared with a particular signal, look up the name in “Signals Listed

Alphabetically” on page 17. It is expected that in any single application a particular pin will always be programmed

to serve the same function. The flexibility of sharing allows a single chip to offer a richer pin selection than would

otherwise be possible.

Initialization Strapping

One group of pins is used as strapped inputs during system reset. These pins function as strapped inputs only

during reset and are used for other functions during normal operation (see “Initialization” on page 65). Note that the

use of these pins for strapping is not considered multiplexing since the strapping function is not programmable.

Pull-Up and Pull-Down Resistors

Pull-up and pull-down resistors are used for strapping during reset and to retain unused or undriven inputs in an

appropriate state. The recommended pull-up value of 3k

Ω to +3.3V and pull-down value of 1kΩ to GND, applies

only to individually terminated signals. To prevent possible damage to the device, I/Os capable of becoming

outputs must never be tied together and terminated through a common resistor.

If your system-level test methodology permits, input-only signals can be connected together and terminated

through either a common resistor or directly to +3.3V or GND. When a resistor is used, its value must ensure that

the grouped I/Os reach a valid logical zero or logical one state when accounting for the total input current into the

PPC405EX.

Table 5. Pin Groups

Group

No. of Pins

Total Signal Pins

246

VDD

17

OVDD

20

EOVDD

6

SVDD

10

GND

71

AVDD

7

AHVDD

2

SAVDD

1

SAGND

1

EAVDD

1

EAGND

1

AGND

4

Total Power Pins

141

Reserved

1

Total Pins

388

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 405EZ | PowerPC 405EZ Embedded Processor |

| 405GPR | Power PC 405GPr Embedded Processor |

| 405GP | Power PC 405GP Embedded Processor |

| 4060120000 | RELAY,MICROSERIES 24 V,1CO |

| 4060EFE | Standalone Linear NiMH/NiCd Fast Battery Charger |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 405EXR | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:Embedded Processor |

| 405EZ | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PowerPC 405EZ Embedded Processor |

| 405F | 功能描述:鼓風(fēng)機(jī) 40x10mm 5VDC 4.7CFM .7W 5400RPM 23dBA SB RoHS:否 制造商:Murata 產(chǎn)品:Blowers 電流類型:DC 電源電壓:5.3 V 氣流:1 l/min 軸承類型: 噪聲: 速度: 功率額定值: 框架尺寸 (mm):20 mm x 20 mm x 1.85 mm 外殼材料: 端接類型:SMD/SMT 系列:MZB |

| 405F | 制造商:ebm-papst Inc 功能描述:FAN 40MM 5VDC |

| 405F/2H | 功能描述:風(fēng)扇 40x40x10mm 5VDC RoHS:否 制造商:Sanyo Denki 產(chǎn)品:Fans 電流類型: 電源電壓:48 V 氣流:636 CFM 軸承類型: 噪聲:83 dBA 速度:6400 RPM 功率額定值:264 W 框架尺寸 (mm):172 mm x 150 mm x 102 mm 外殼材料:Aluminum 端接類型:Wire 系列: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。