- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67328 > 5962-8967901QX (MAXIM INTEGRATED PRODUCTS INC) 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 PDF資料下載

參數(shù)資料

| 型號: | 5962-8967901QX |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

| 封裝: | CERAMIC, DIP-40 |

| 文件頁數(shù): | 10/30頁 |

| 文件大小: | 4271K |

| 代理商: | 5962-8967901QX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

MAX5813/MAX5814/MAX5815

Ultra-Small, Quad-Channel, 8-/10-/12-Bit Buffered

Output DACs with Internal Reference and I2C Interface

18

Maxim Integrated

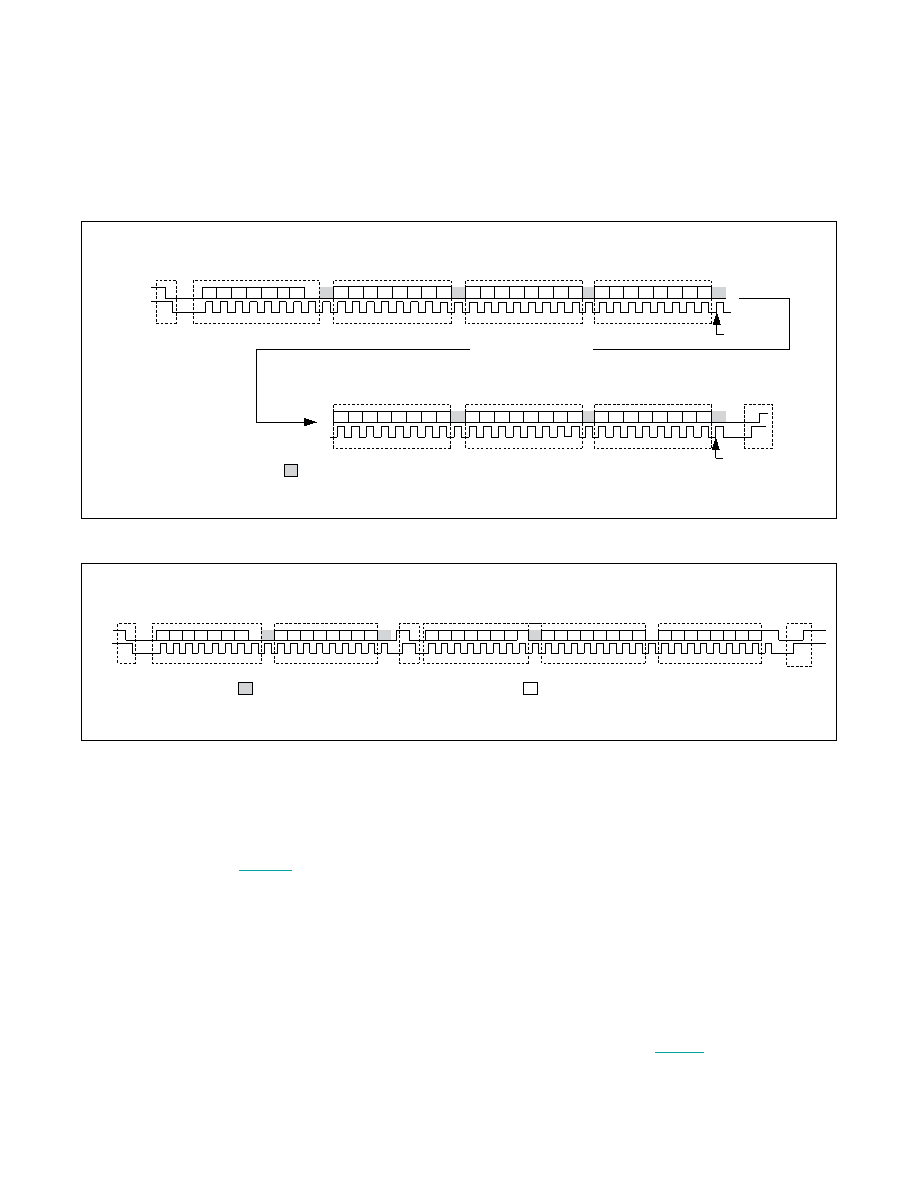

Figure 5. Multiple Register Write Sequence (Standard I2C Protocol)

Figure 6. Standard I2C Register Read Sequence

Combined Format I2C Readback Operations

Each readback sequence is framed by a START or

Repeated START condition and a STOP condition. Each

word is 8 bits long and is followed by an acknowledge

clock pulse as shown in Figure 6. The first byte contains

the address of the MAX5813/MAX5814/MAX5815 with

R/W = 0 to indicate a write. The second byte contains

the register that is to be read back. There is a Repeated

START condition, followed by the device address with

R/W = 1 to indicate a read and an acknowledge clock.

The master has control of the SCL line but the MAX5813/

MAX5814/MAX5815 take over the SDA line. The final two

bytes in the frame contain the register data readback

followed by a STOP condition. If additional bytes beyond

those required to readback the requested data are pro-

vided, the MAX5813/MAX5814/MAX5815 will continue to

readback ones.

Readback of individual CODE registers is supported for

the CODE command (B[23:20] = 0000). For this com-

mand, which supports a DAC address, the requested

channel CODE register content will be returned; if all

DACs are selected, CODEA content will be returned.

Readback of individual DAC registers is supported for

all LOAD commands (B[23:20] = 0001, 0010, or 0011).

For these commands, which support a DAC address, the

requested DAC register content will be returned. If all

DACs are selected, DACA content will be returned.

Modified readback of the POWER register is supported

for the POWER command (B[23:20] = 0100). The power

status of each DAC is reported in locations B[3:0], with a

1 indicating the DAC is powered down and a 0 indicating

the DAC is operational (see Table 3).

SCL

A

W

20 19 18 17

A

16

15 14 13 12 11 10 9A

8

START

SDA

WRITE ADDRESS

BYTE #1: I2C SLAVE ADDRESS*

WRITE COMMAND1

BYTE #2: COMMAND1 BYTE

(B[23:16])

WRITE DATA1

BYTE #3: DATA1 HIGH BYTE

(B[15:8])

21

0 0 1 A3 A2 A1 A0

22

23

STOP

7 6 5 4 3 2 1A

0

WRITE DATA1

BYTE #4: DATA1 LOW BYTE

(B[7:0])

20 19 18 17

A

16

15 14 13 12 11 10 9A

8

21

22

23

7 6 5 4 3 2 1A

0

ADDITIONAL COMMAND AND

DATA PAIRS (3 BYTE BLOCKS)

COMMAND1

EXECUTED

COMMANDn

EXECUTED

BYTE #5: COMMANDn BYTE

(B[23:16])

BYTE #6: DATAn HIGH BYTE

(B[15:8])

BYTE #7: DATAn LOW BYTE

(B[7:0])

*I2C SLAVE ADDRESS FOR THE TSSOP PACKAGE IS USED

ACK. GENERATED BY MAX5813/MAX5814/MAX5815

A

READ DATA

BYTE #4: DATA 1 HIGH

BYTE (B[15:8])

READ DATA

BYTE #5: DATA 1 LOW

BYTE (B[7:0])

REPEATED

START

READ ADDRESS

BYTE #3: I2C SLAVE

ADDRESS*

WRITE ADDRESS

BYTE #1: I2C SLAVE

ADDRESS*

WRITE COMMAND 1

BYTE #2: COMMAND 1

BYTE

*I2C SLAVE ADDRESS FOR THE TSSOP PACKAGE IS USED

ACK. GENERATED BY MAX5813/MAX5814/ MAX5815

ACK. GENERATED BY I2C MASTER

A

START

STOP

SCL

SDA

00 1A3A2A1A0W A

A

0 0N

0 01 A3 A2 A1 A0 RA D DDD DD DD

DDDDDDDD ~A

A

NN NNN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-8967901XX | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8968303HZA | 1-OUTPUT 15 W DC-DC REG PWR SUPPLY MODULE |

| 5962-9158001HZA | 1-OUTPUT 20 W DC-DC REG PWR SUPPLY MODULE |

| 5962-9162501HZA | 1-OUTPUT 20 W DC-DC REG PWR SUPPLY MODULE |

| 5962-8968301HXA | 1-OUTPUT 15 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-8967901XC | 制造商:SEI 功能描述: |

| 5962-89680012A | 制造商:Texas Instruments 功能描述:Octal Transmitter/Receiver 20-Pin LCCC Tube |

| 5962-89680012A-T | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| 5962-8968001RA | 制造商:Texas Instruments 功能描述:Octal Transmitter/Receiver 20-Pin CDIP Tube 制造商:Texas Instruments 功能描述:LINE TRNSCVR 8TR 8TX 8RX 20CDIP - Rail/Tube |

| 5962-8968001SA | 制造商:Texas Instruments 功能描述:Octal Transmitter/Receiver 20-Pin CFPAK Tube 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。