- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382811 > 71V433S12PFI (Integrated Device Technology, Inc.) 32K x 32 3.3V Synchronous SRAM Flow-Through Outputs PDF資料下載

參數(shù)資料

| 型號: | 71V433S12PFI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | 32K x 32 3.3V Synchronous SRAM Flow-Through Outputs |

| 中文描述: | 32K的× 32 3.3同步SRAM的流量通過輸出 |

| 文件頁數(shù): | 9/19頁 |

| 文件大小: | 261K |

| 代理商: | 71V433S12PFI |

6.42

IDT71V433

32K x 32, 3.3V Synchronous SRAM with Flow-Through Outputs Commercial and Industrial Temperature Ranges

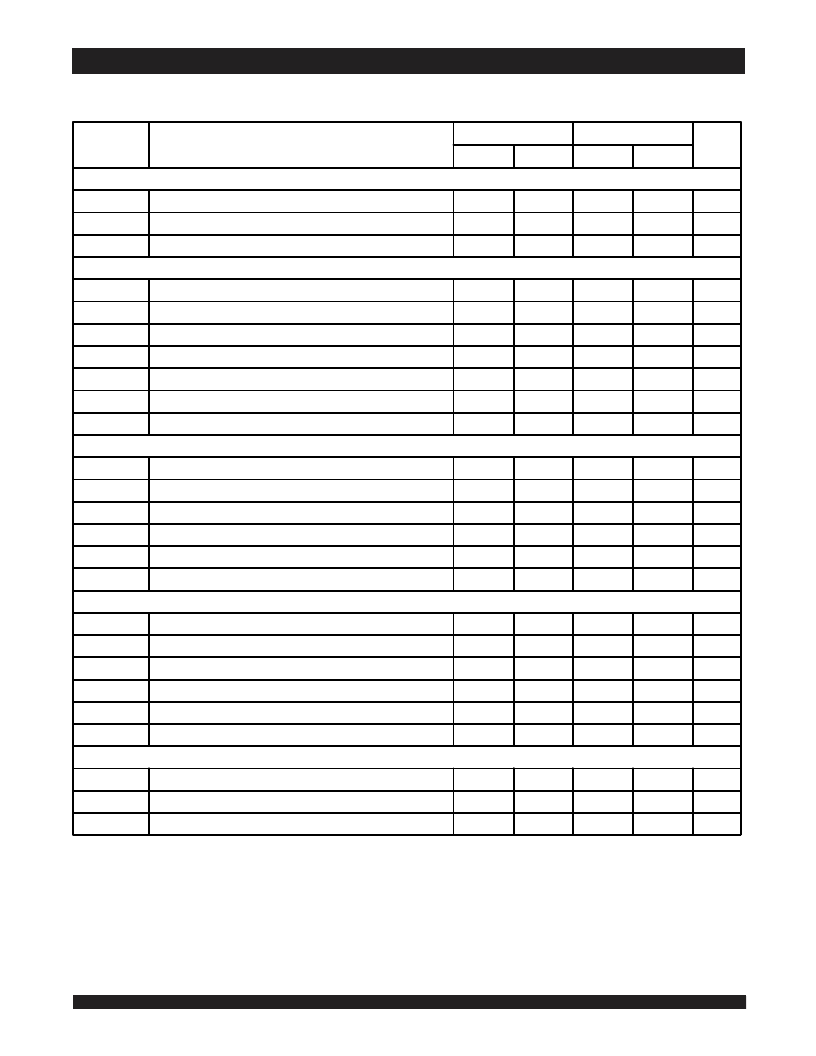

AC Electrical Characteristics

(V

DD

= 3.3V +10/-5%, Commercial and Industrial Temperature Ranges)

Symbol

Parameter

71V433S11

71V433S12

Unit

Min.

Max.

Min.

Max.

Clock Parameters

t

CYC

Clock Cycle Time

20

____

20

____

ns

t

CH

(1)

Clock High Pulse Width

6

____

6

____

ns

t

CL

(1)

Clock Low Pulse Width

6

____

6

____

ns

Output Parameters

t

CD

Clock High to Valid Data

____

11

____

12

ns

t

CDC

Clock High to Data Change

3

____

3

____

ns

t

CLZ

(2)

Clock High to Output Active

0

____

0

____

ns

t

CHZ

(2)

Clock High to Data High-Z

3

6

3

6

ns

t

OE

Output Enable Access Time

____

4

____

4

ns

t

OLZ

(2)

Output Enable Low to Data Active

0

____

0

____

ns

t

OHZ

(2)

Output Enable High to Data High-Z

____

6

____

6

ns

Setup Times

t

SA

Address Setup Time

2.5

____

2.5

____

ns

t

SS

Address Status Setup Time

2.5

____

2.5

____

ns

t

SD

Data in Setup Time

2.5

____

2.5

____

ns

t

SW

Write Setup Time

2.5

____

2.5

____

ns

t

SAV

Address Advance Setup Time

2.5

____

2.5

____

ns

t

SC

Chip Enable/Select Setup Time

2.5

____

2.5

____

ns

Hold Times

t

HA

Address Hold Time

0.5

____

0.5

____

ns

t

HS

Address Status Hold Time

0.5

____

0.5

____

ns

t

HD

Data In Hold Time

0.5

____

0.5

____

ns

t

HW

Write Hold Time

0.5

____

0.5

____

ns

t

HAV

Address Advance Hold Time

0.5

____

0.5

____

ns

t

HC

Chip Enable/Select Hold Time

0.5

____

0.5

____

ns

Sleep Mode and Configuration Parameters

t

ZZPW

ZZ Pulse Width

100

____

100

____

ns

t

ZZR

(3)

ZZ Recovery Time

100

____

100

____

ns

t

CFG

(4)

Configuration Set-up Time

80

____

80

____

ns

3729 tbl 15

NOTES:

1. Measured as HIGH above 2.0V and LOW below 0.8V.

2. Transition is measured ±200mV fromsteady-state.

3. Device must be deselected when powered-up fromsleep mode.

4. t

CFG

is the mnimumtime required to configure the device based on the

LBO

input.

LBO

is a static input and must not change during normal operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7207 | T-1 Subminiature Lamps |

| 7200 | T-1 Subminiature Lamps |

| 7201 | T-1 Subminiature Lamps |

| 7203 | T-1 Subminiature Lamps |

| 7205 | T-1 Subminiature Lamps |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71V546S100PF | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 4.5M-Bit 128K x 36 5ns 100-Pin TQFP Tray |

| 71V546S100PF8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 4.5M-Bit 128K x 36 5ns 100-Pin TQFP T/R |

| 71V546S100PFG | 功能描述:靜態(tài)隨機存取存儲器 128Kx36 ZBT SYNC 3.3V PIPELINED 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V546S100PFG8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Single 3.3V 4.5M-Bit 128K x 36 5ns 100-Pin TQFP T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC SGL 3.3V 4.5MBIT 128KX36 5NS 100TQFP - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:128Kx36 ZBT SYNC 3.3V PIPELINED SRAM |

| 71V546S100PFGI | 功能描述:靜態(tài)隨機存取存儲器 128Kx36 ZBT SYNC 3.3V PIPELINED 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。