- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16278 > 78Q2120C09-DB (Maxim Integrated Products)BOARD DEMO 78Q2120C PDF資料下載

參數(shù)資料

| 型號(hào): | 78Q2120C09-DB |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 5/35頁 |

| 文件大?。?/td> | 0K |

| 描述: | BOARD DEMO 78Q2120C |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

78Q2120C

10/100BASE-TX

Transceiver

Page: 13 of 35

2009 Teridian Semiconductor Corporation

Rev 1.3

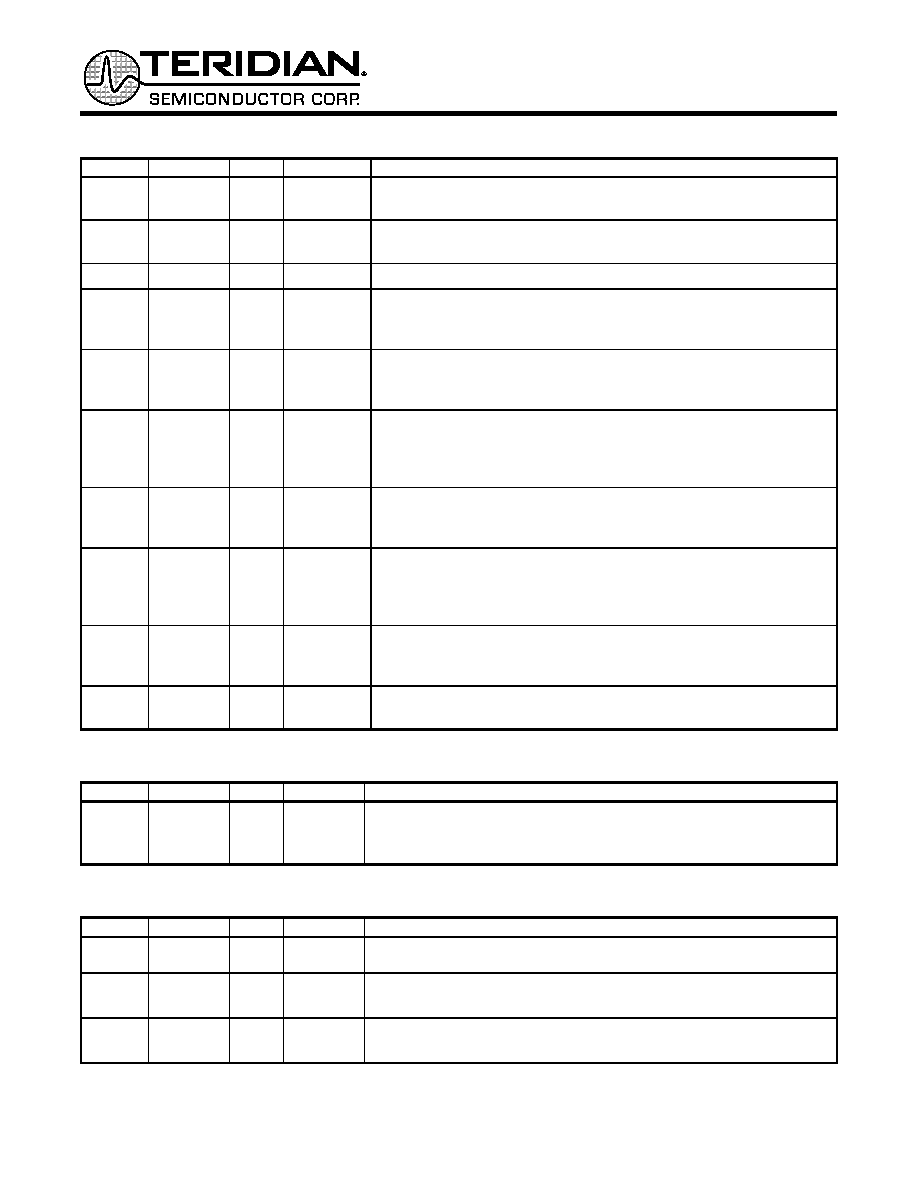

MR1: Status Register

BIT

SYMBOL TYPE DEFAULT DESCRIPTION

1.9

100T2_H

R

0

100BASE-T2 Half Duplex Ability:

Reads ‘0’ to indicate the

78Q2120C does not support 100Base-T2 full duplex mode.

1.8

EXTS

R

0

Extended Status Information Availability: Reads ‘0’ to indicate the

78Q2120C does not support Extended Status information on MR15.

1.7

RSVD

R

0

Reserved

1.6

MFPS

R

0

Management Frame Preamble Suppression Support:

A “0”

indicates that the 78Q2120C can read management frames with a

preamble.

1.5

ANEGC

R

0

Auto-Negotiation Complete: A logic one indicates that the Auto-

Negotiation process has been completed, and that the contents of

registers MR4,5,6 are valid.

1.4

RFAULT

RC

0

Remote Fault: A logic one indicates that a remote fault condition

has been detected and remains set until it is cleared. This bit can

only be cleared by reading this register (MR1) via the management

interface.

1.3

ANEGA

R

(1)

Auto-Negotiation Ability: When set, this bit indicates the device’s

ability to perform Auto-Negotiation.

The value of this bit is

determined by the ANEGEN bit (MR0.12).

1.2

LINK

R

0

Link Status:

A logic one indicates that a valid link has been

established. If the link status should transition from an OK status to

a NOT-OK status, this bit will become cleared and remains cleared

until it is read.

1.1

JAB

RC

0

Jabber Detect: In 10Base-T mode, this bit is set during a jabber

event. After a jabber event, the bit remains set until cleared by a

read operation.

1.0

EXTD

R

1

Extended Capability: Reads ’1’ to indicate the 78Q2120C provides

an extended register set (MR2 and beyond).

MR2: PHY Identifier Register 1

BIT

SYMBOL TYPE

VALUE

DESCRIPTION

2.15:0

OUI

[23:6]

R

000Eh

Organizationally Unique Identifier:

This value is 00-C0-39 for

TERIDIAN Semiconductor Corporation. This register contains the

first 16-bits of the identifier.

MR3: PHY Identifier Register 2

BIT

SYMBOL TYPE

VALUE

DESCRIPTION

3.15:10

OUI

[5:0]

R

1Ch

Organizationally Unique Identifier: Remaining 6 bits of the OUI.

3.9:4

MN

R

0Ch

Model Number: The last 2 digits of the model number 78Q2120C are

encoded into the 6 bits.

3.3:0

RN

R

9h

Revision Number: The value ‘1001’ corresponds to the ninth revision

of the silicon.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NCP301LSN45T1G | IC DETECTOR VOLTAGE 4.5V 5TSOP |

| MAX810TTRG | IC MPU SUPERVISORY 3.08V SOT23 |

| UCY2V101MHD3TN | CAP ALUM 100UF 350V 20% RADIAL |

| MAX5422EVKIT+ | KIT EVLAUTION MAX5422/23/24 |

| NCP303LSN45T1G | IC DETECTOR VOLTAGE 4.5V 5TSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 78Q2120-CGT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:10/100BASE-TX Ethernet Transceiver |

| 78Q2123 | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:10/100BASE-TX Transceiver |

| 78Q2123/F | 功能描述:以太網(wǎng) IC 10/100 Fast Ethernet MicroPHY RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| 78Q2123/F1 | 功能描述:以太網(wǎng) IC RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| 78Q2123CGV/F | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:10/100BASE-TX Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。