- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378217 > 82C51A (OKI SEMICONDUCTOR CO., LTD.) UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER PDF資料下載

參數(shù)資料

| 型號(hào): | 82C51A |

| 廠商: | OKI SEMICONDUCTOR CO., LTD. |

| 英文描述: | UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER |

| 中文描述: | 通用同步異步收發(fā)器 |

| 文件頁數(shù): | 18/26頁 |

| 文件大小: | 203K |

| 代理商: | 82C51A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

18/26

Semiconductor

MSM82C51A-2RS/GS/JS

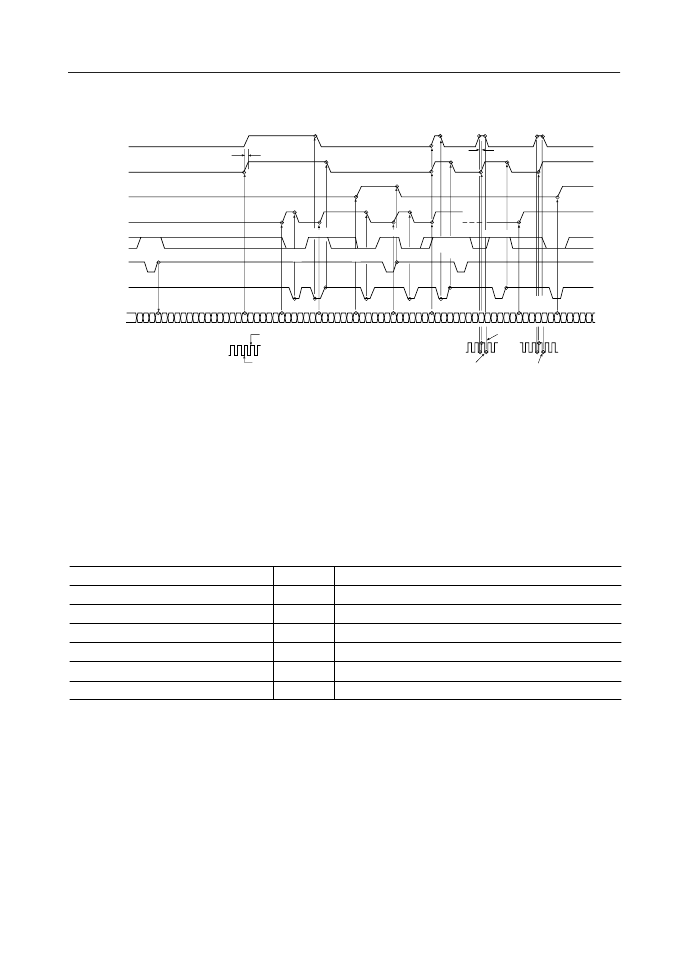

Receiver Control and Flag Timing (SYNC Mode)

x x x x x x 0 1 2 3 4

0 1 2 3 4

PAR

PAR

PAR

PAR

PAR

PAR

x x x x x x x

PAR

0 1 2 3 4

PAR

SYNDET

(Pin) (Note 1)

SYNDET (SB)

OVERRUN

ERROR (SB)

RXRDY (PIN)

C/

D

WR

RD

RXD

Don't

Care

SYNC

SYNC

Data

CHAR 1

Data

Data

CHAR 3

SYNC

SYNC

Don't Care

Data

Data

ETC

CHAR ASSY Begins

Exit Hunt Mode

Set SYNDET

Exit Hunt Mode

Set SYNDET (Status bit)

Set SYNDET (Status bit)

CHAR ASSY

Begins

Wr EH

RxEn

Rd Data

Rd Status

Wr Err Res

Rd Data

Rd SYNC

Rd Status

Rd Status

Data

t

IS

t

ES

(Note 2)

Note:

PAR

1. Internal Synchronization is based on the case of 5 data bit length + parity bit and 2 synchronous charactor.

2. External Synchronization is based on the case of 5 data bit length + parity bit.

Note:

1. Half-bit processing for the start bit

When the MSM82C51A-2 is used in the asynchronous mode, some problems are

caused in the processing for the start bit whose length is smaller than the 1-data bit

length. (See Fig. 1.)

2. Parity flag after a break signal is received (See Fig. 2.)

When the MSM82C51A-2 is used in the asynchrous mode, a parity flag may be set

when the next normal data is read after a break signal is received.

A parity flag is set when the rising edge of the break signal (end of the break signal)

is changed between the final data bit and the parity bit, through a RXRDY signal may

not be outputted.

If this occurs, the parity flag is left set when the next normal dats is received, and the

received data seems to be a parity error.

Smaller than 7-Receiver Clock Length

Smaller than 31-Receiver Clock Length

8-Receiver Clock Length

32-Receiver Clock Length

9 to 16-Receiver Clock Length

33 to 64-Receiver Clock Length

¥

16

¥

64

¥

16

¥

64

¥

16

¥

64

Start bit Length

Mode

Operation

The short start bit is ignored. (Normal)

The short start bit is ignored. (Normal)

Data cannot be received correctly due to a malfunction.

Data cannot be received correctly due to a malfunction.

The bit is regarded as a start bit. (normal)

The bit is regarded as a start bit. (normal)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 82C52 | CMOS Serial Controller Interface |

| 82C59A | CMOS Priority Interrupt Controller |

| 82C79 | PROGRAMMABLE KEYBOARD / DISPLAY INTERFACE |

| 82C82 | CMOS Octal Latching Bus Driver |

| 82C84 | CMOS Clock Generator Driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82C52 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS Serial Controller Interface |

| 82C52_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS Serial Controller Interface |

| 82C53 | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:VOLTAGE DETECTORS |

| 82C54 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:CHMOS PROGRAMMABLE INTERVAL TIMER |

| 82C54/BJA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Timer Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。