- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄36334 > 935243450557 (NXP SEMICONDUCTORS) COLOR SIGNAL ENCODER, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | 935243450557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL ENCODER, PQFP44 |

| 封裝: | PLASTIC, SOT-307, QFP-44 |

| 文件頁(yè)數(shù): | 19/35頁(yè) |

| 文件大小: | 261K |

| 代理商: | 935243450557 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

1997 Jan 06

26

Philips Semiconductors

Preliminary specication

Digital Video Encoder (ConDENC)

SAA7120; SAA7121

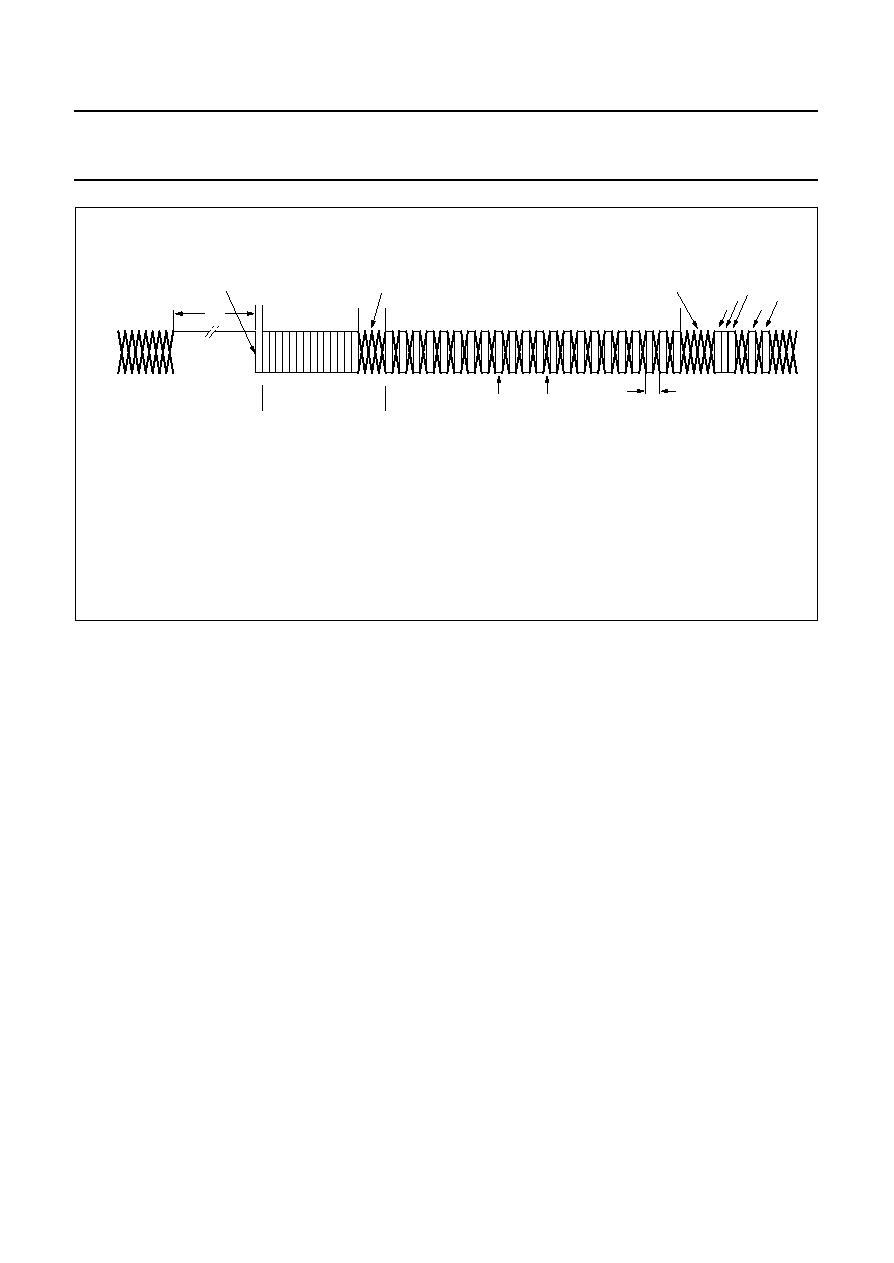

Fig.10 RTCI timing.

handbook, full pagewidth

128

13

14

19

67

69 72 74

68

01

0

21

RTCI

HPLL

increment

FSCPLL increment (1)

H/L transition

count start

4 bits

reserved (7)

valid

sample

invalid

sample

not used in SAA7120/21

5 bits

reserved (7)

8/LLC

MBH789

LOW

time slot:

(2)

(3)

(5)

(6)

(4)

(3) Reset bit: only from SAA7111 decoder.

(4) FISE bit: 0 = 50 Hz, 1 = 60 Hz.

(5) Odd/even bit: odd/even from external.

(6) Colour detection: 0 = no colour detected, 1 = colour detected.

(7) Reserved bits: 232 with 50 Hz systems, 229 with 60 Hz systems.

(1) SAA7111 provides (22:0) bits, resulting in 3 reserved bits before

sequence bit.

(2) Sequence bit

PAL: 0 = (R

Y) line normal, 1 = (RY) line inverted

NTSC: 0 = no change.

Explanation of RTCI data bits

1. The ConDENC generates the subcarrier frequency out

of the FSCPLL increment if enabled (see item 6.).

2. The PAL bit indicates the line with inverted R - Y

component of colour difference signal.

3. If the reset bit is enabled

(RTCE = 1; DECPH = 1; PHRES = 00), the phase of

the subcarrier is reset in each line whenever the reset

bit of RTCI input is set to 1.

4. If the FISE bit is enabled (RTCE = 1; DECFIS = 1), the

ConDENC takes this bit instead of the FISE bit in

subaddress 61H.

5. If the odd/even bit is enabled (RTCE = 1; DECOE = 1),

the ConDENC ignores its internally generated

odd/even flag and takes the odd/even bit from RTCI

input.

6. If the colour detection bit is enabled (RTCE = 1;

DECCOL = 1) and no colour was detected (colour

detection bit = 0), the subcarrier frequency is

generated by the ConDENC. In the other case (colour

detection bit = 1) the subcarrier frequency is evaluated

out of FSCPLL increment.

If the colour detection bit is disabled (RTCE = 1;

DECCOL = 0), the subcarrier frequency is evaluated

out of FSCPLL increment, independent of the colour

detection bit of RTCI input.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935243460551 | COLOR SIGNAL ENCODER, PQFP44 |

| 935243460557 | COLOR SIGNAL ENCODER, PQFP44 |

| 935264425518 | COLOR SIGNAL ENCODER, PQFP44 |

| 935264425551 | COLOR SIGNAL ENCODER, PQFP44 |

| 935264425557 | COLOR SIGNAL ENCODER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935245650125 | 制造商:NXP Semiconductors 功能描述:Inverter 1-Element CMOS 5-Pin TSSOP T/R |

| 935248-90 | 制造商:JANCO 功能描述:935248-90 |

| 9-3525-012 | 制造商:KEYSTONE 功能描述:MODIFIED 3525,VERSION E |

| 935252-5 | 制造商:C-H 功能描述:935252-5 |

| 935257650112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY ICSUBS TO 935257650112 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。