- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36460 > 9402AVK (MICRONAS SEMICONDUCTOR HOLDING AG) SPECIALTY CONSUMER CIRCUIT, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | 9402AVK |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | 14 X 14 MM, 2 MM HEIGHT, PLASTIC, MS-022, MQFP-80 |

| 文件頁數(shù): | 46/126頁 |

| 文件大?。?/td> | 1673K |

| 代理商: | 9402AVK |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

DATA SHEET

26

Aug. 16, 2004; 6251-552-1DS

Micronas

2.5.3. Coarse and Fine Delay

Before digital-to-analog conversion an adjustment of

the phase of the luminance is performed. A coarse

delay from

8 to +7 in steps of 1 pixel CLKB36

(~28 ns) is possible (COARSEDEL). FINEDEL shifts

the luminance one CLKB72 (~14 ns) pixel. This can be

used to compensate delays, if the external processing

of Y and UV produces different delays (e.g. external

lowpass filtering).

2.5.4. Oversampling and DAC

After conversion into 8:8:8 format (CLKB72=72 MHz),

three 9-bit digital-to-analog converters are used for

analog YUV output. This twofold-oversampling gener-

ates 1920 active pixels per line (when using recom-

mended settings) and simplifies the external postfilter-

ing. The output voltage is determined by PKLY, PKLU

and PKLV and can be set in a range of 0.4 V ...1.9 V

(fullscale).

8 bits of the luminance D/A converter are used for the

entire signal. The 9th bit is used for over- and under-

shoots caused by the peaking to prevent or reduce

clipping artifacts. As the CTI block seldomly produces

such overshoots, a full-scale operation can be acti-

vated by CHROMAMP. The output voltages may be

calculated by:

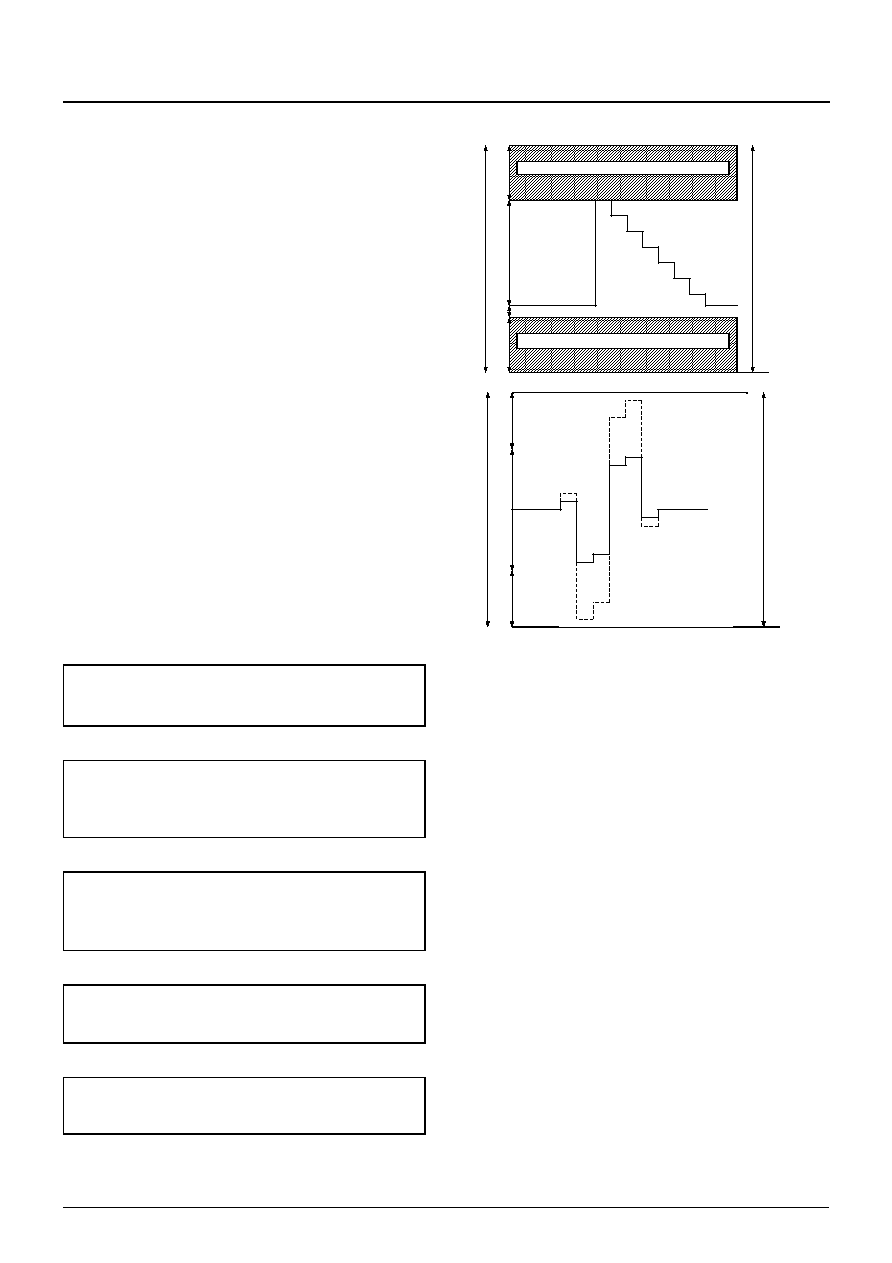

Fig. 2–36: DAC Output Signals

2.5.5. Output-Sync Controller

The output sync controller generates horizontal and

vertical synchronization signals for the scanrate-con-

verted output signal.

The number of pixels per line is 4*PPLOP. The default

value

of

288

results

in

1152

pixels/line.

With

CLKB= 36 MHz, the horizontal output frequency is

31.25 kHz, which is twice the PAL horizontal fre-

quency. Out of these pixels, 16*APPLOP are displayed

as active picture area, which are 960 by default. The

position on the screen depends on the NAPPLOP. It

marks the picture area not active in horizontal direction

and moves the active picture in horizontal direction.

The number of lines per field is 2*LPFOP. This value is

only used in the vertical freeruning mode. In vertical

locked mode, the number of lines per field is derived

from the CVBS signal itself and not adjustable. The

active and non-active picture areas are marked by

ALPFOP and NALPFOP, respectively.

Both generators have a so called ‘locked-mode’ and

‘freeruning-mode’. Not all combinations of these

modes make sense. Table 2–13 on page 27 shows

ingenious configurations.

[for unpeaked signals max.]

[for peaked signals max.]

VoltageY

1.56V

PKLY

256

---------------

0.36V

+

signalY

=

signalY

160....400

512

------------------------

=

signalY

0....511

512

------------------

=

VoltageU V

,

1.56V

PKLU V

,

256

-----------------------

0.36V

+

CHROMAMP signalUV

=

signalUV

128....384

512

------------------------

=

0 V

16 LSB

240 LSB normal

signal range

'black'

max

.1.9

V

m

ax

.0.9

V

PKLY

128 LSB upper headroom for peaking

128 LSB lower headroom for peaking

9

b

itco

nv

ersi

on

ra

ng

e

'no color'

max.

1.9

V

PKLU

PLLV

9b

itconver

sion

r

ange

ma

x.

0.95

V

CHROMAMP=1

CHROMAMP=0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 94136-608T | 72 CONTACT(S), FEMALE, 40 DEGREE SINGLE PART CARD EDGE CONN, SOLDER, SOCKET |

| 94136-608 | 72 CONTACT(S), FEMALE, 40 DEGREE SINGLE PART CARD EDGE CONN, SOLDER, SOCKET |

| 94136-613K | 72 CONTACT(S), FEMALE, 40 DEGREE SINGLE PART CARD EDGE CONN, SOLDER, SOCKET |

| 94136-803K | 72 CONTACT(S), FEMALE, 40 DEGREE SINGLE PART CARD EDGE CONN, SOLDER, SOCKET |

| 94136-803T | 72 CONTACT(S), FEMALE, 40 DEGREE SINGLE PART CARD EDGE CONN, SOLDER, SOCKET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9402F | 制造商:HH SMITH 功能描述:HARDWARE |

| 9402H | 制造商:Abbatron/HH Smith 功能描述: |

| 9402L | 制造商:Abbatron/HH Smith 功能描述: |

| 9402M | 制造商:Abbatron/HH Smith 功能描述: |

| 940-2MM | 功能描述:支架與墊片 Plastic Spcr 2mm Nylon White RoHS:否 制造商:Schurter 類型:Transipillar Spacers 長度:16 m 螺紋大小:M4 外徑:10 mm 材料:Nylon with Steel 電鍍:Zinc |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。