- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25566 > 9FG108CGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | 9FG108CGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 6.10 MM WIDTH, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-48 |

| 文件頁數(shù): | 16/21頁 |

| 文件大小: | 263K |

| 代理商: | 9FG108CGLFT |

IDTTM/ICSTM

Frequency Generator for CPU, FBD, PCIe Gen 1/2 & SATA

ICS9FG108

REV J 02/20/09

ICS9FG108

Frequency Generator for CPU, FBD, PCIe Gen 1/2 & SATA

4

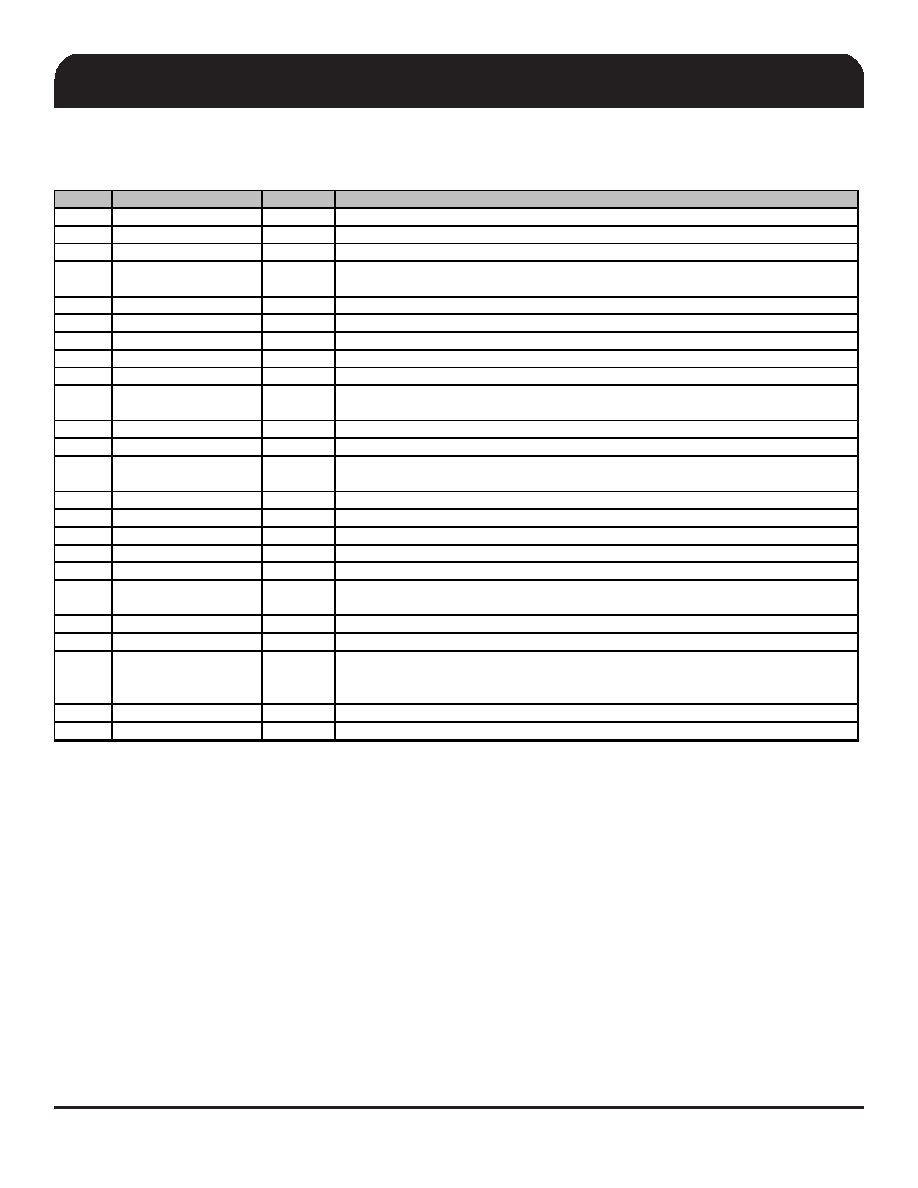

Pin Description (continued)

PIN #

PIN NAME

PIN TYPE

DESCRIPTION

25

DIF_STOP#

IN

Active low input to stop differential output clocks.

26

**SPREAD

IN

Asynchronous, active high input to enable spread spectrum functionality.

27

*SEL14M_25M#

IN

Select 14.31818 MHz or 25 Mhz input frequency. 1 = 14.31818 MHz, 0 = 25 MHz

28

**OE_3

IN

Active high input for enabling output 3.

0 = tri-state outputs, 1= enable outputs

29

DIF_3#

OUT

0.7V differential Complementary clock output

30

DIF_3

OUT

0.7V differential true clock output

31

VDD

PWR

Power supply, nominal 3.3V

32

DIF_2#

OUT

0.7V differential Complementary clock output

33

DIF_2

OUT

0.7V differential true clock output

34

*OE_2

IN

Active high input for enabling output 2.

0 = tri-state outputs, 1= enable outputs

35

GND

PWR

Ground pin.

36

VDD

PWR

Power supply, nominal 3.3V

37

*OE_1

IN

Active high input for enabling output 1.

0 = tri-state outputs, 1= enable outputs

38

DIF_1#

OUT

0.7V differential Complementary clock output

39

DIF_1

OUT

0.7V differential true clock output

40

VDD

PWR

Power supply, nominal 3.3V

41

DIF_0#

OUT

0.7V differential Complementary clock output

42

DIF_0

OUT

0.7V differential true clock output

43

**OE_0

IN

Active high input for enabling output 0.

0 = tri-state outputs, 1= enable outputs

44

**FS1

I/O

Frequency select pin.

45

**FS0

IN

Frequency select pin.

46

IREF

OUT

This pin establishes the reference current for the differential current-mode output

pairs. This pin requires a fixed precision resistor tied to ground in order to establish

the appropriate current. 475 ohms is the standard value.

47

GNDA

PWR

Ground pin for the PLL core.

48

VDDA

PWR

3.3V power for the PLL core.

Note:

* indicates internal 120K pull up

** indicates internal 120K pull down

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9FG108DFLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG108DFILF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG108DGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG108DGLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG1200DF-1LFT | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9FG108DFILF | 功能描述:時鐘合成器/抖動清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DFILFT | 功能描述:時鐘合成器/抖動清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DFLF | 功能描述:時鐘合成器/抖動清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DFLFT | 功能描述:時鐘合成器/抖動清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DGILF | 功能描述:時鐘合成器/抖動清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。