- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25566 > 9FG108CGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | 9FG108CGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 6.10 MM WIDTH, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-48 |

| 文件頁數(shù): | 4/21頁 |

| 文件大小: | 263K |

| 代理商: | 9FG108CGLFT |

IDTTM/ICSTM

Frequency Generator for CPU, FBD, PCIe Gen 1/2 & SATA

ICS9FG108

REV J 02/20/09

ICS9FG108

Frequency Generator for CPU, FBD, PCIe Gen 1/2 & SATA

12

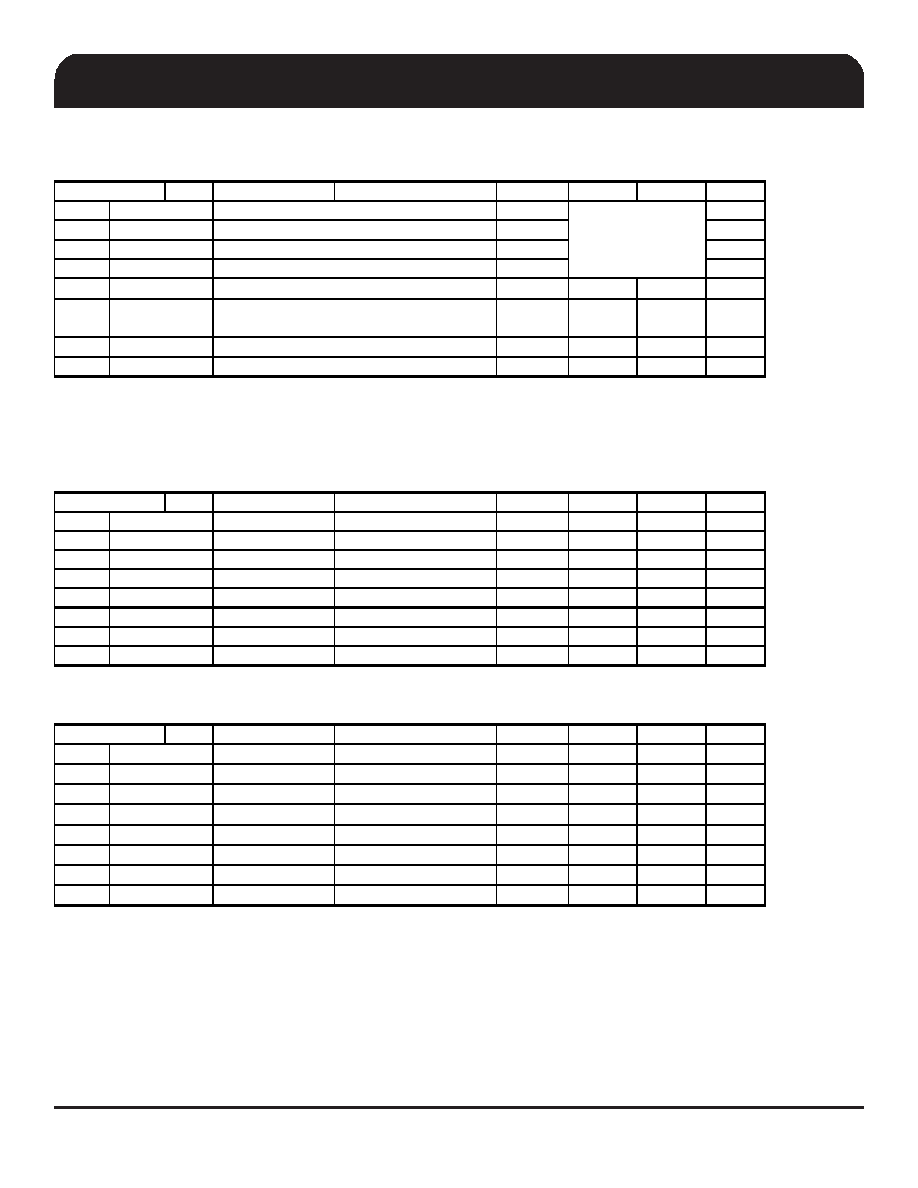

SMBus Table: Device Control Register, READ/WRITE ADDRESS (DC/DD)

Pin #

Name

Control Function

Type

0

1

Default

Bit 7

RW

Pin 27

Bit 6

RW

Pin 5

Bit 5

RW

Pin 44

Bit 4

RW

Pin 7

Bit 3

RW

Off

On

Pin 26

Bit 2

RW

Hardware

Select

Software

Select

0

Bit 1

RW

Driven

Hi-Z

0

Bit 0

RW

Down

Center

0

Notes:

1. These bits reflect the state of the corresponding pins at power up, but may be written to

if Byte 0, bit 2 is set to '1'. FS3 is the SEL14M_25M# pin.

SMBus Table: Output Enable Register

Pin #

Name

Control Function

Type

0

1

Default

Bit 7

DIF_7 EN

Output Enable

RW

Disable

Enable

1

Bit 6

DIF_6 EN

Output Enable

RW

Disable

Enable

1

Bit 5

DIF_5 EN

Output Enable

RW

Disable

Enable

1

Bit 4

DIF_4 EN

Output Enable

RW

Disable

Enable

1

Bit 3

DIF_3 EN

Output Enable

RW

Disable

Enable

1

Bit 2

DIF_2 EN

Output Enable

RW

Disable

Enable

1

Bit 1

DIF_1 EN

Output Enable

RW

Disable

Enable

1

Bit 0

DIF_0 EN

Output Enable

RW

Disable

Enable

1

Note:

SMBus Table: Output Stop Mode Register

Pin #

Name

Control Function

Type

0

1

Default

Bit 7

DIF_7 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

Bit 6

DIF_6 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

Bit 5

DIF_5 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

Bit 4

DIF_4 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

Bit 3

DIF_3 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

Bit 2

DIF_2 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

Bit 1

DIF_1 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

Bit 0

DIF_0 STOP EN Free Run/ Stop Enable

RW

Free-run Stop-able

0

See Frequency

Selection Table,

Page 1

FS3

1

FS2

1

FS1

1

FS0

1

-

Byte 2

-

Byte 1 sets outputs active or inactive, not the conditons set by the OE inputs.

-

Byte 1

-

DIF_STOP# drive mode

-

Spread Type

26

Spread Enable

1

-

Enable Software Control of Frequency,

Spread Enable (Spread Type always

44

7

Byte 0

27

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9FG108DFLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG108DFILF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG108DGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG108DGLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9FG1200DF-1LFT | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9FG108DFILF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DFILFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DFLF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DFLFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9FG108DGILF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 PCIE GEN2 SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。