- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4348 > A1460A-1TQG176I (Microsemi SoC)IC FPGA 6K GATES 176-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | A1460A-1TQG176I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 7/90頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 6K GATES 176-TQFP |

| 標(biāo)準(zhǔn)包裝: | 40 |

| 系列: | ACT™ 3 |

| LAB/CLB數(shù): | 848 |

| 輸入/輸出數(shù): | 151 |

| 門數(shù): | 6000 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 176-LQFP |

| 供應(yīng)商設(shè)備封裝: | 176-TQFP(24x24) |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

Accelerator Series FPGAs – ACT 3 Family

R e visio n 3

2 -7

Antifuse Connections

An antifuse is a “normally open” structure as opposed to the normally closed fuse structure used in

PROMs or PALs. The use of antifuses to implement a programmable logic device results in highly

testable structures as well as an efficient programming architecture. The structure is highly testable

because there are no preexisting connections; temporary connections can be made using pass

transistors. These temporary connections can isolate individual antifuses to be programmed as well as

isolate individual circuit structures to be tested. This can be done both before and after programming. For

example, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the

functionality of all logic modules can be verified.

Four types of antifuse connections are used in the routing structure of the ACT 3 array. (The physical

structure of the antifuse is identical in each case; only the usage differs.)

Table 2-1 shows four types of antifuses.

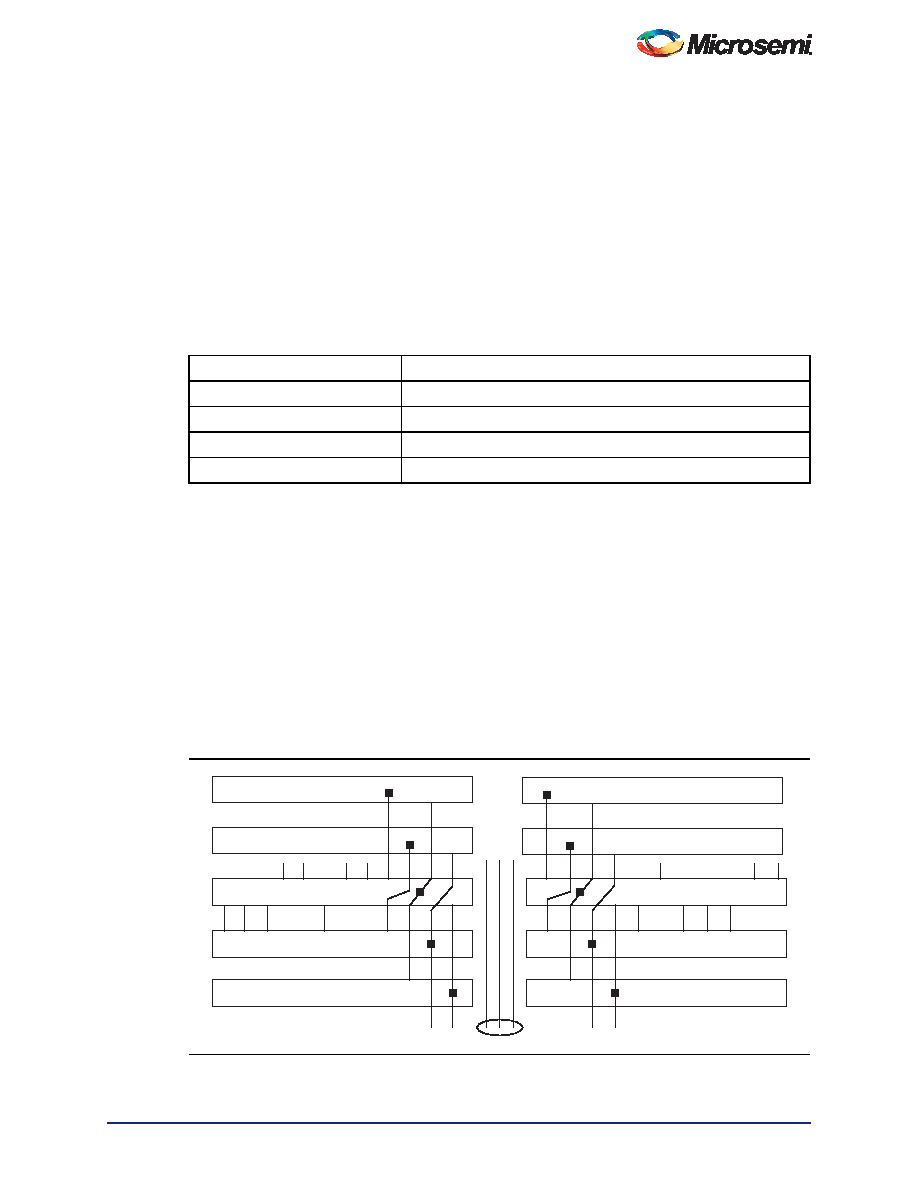

Examples of all four types of connections are shown in Figure 2-7 on page 2-6 and Figure 2-8 on

Module Interface

Connections to Logic and I/O modules are made through vertical segments that connect to the module

inputs and outputs. These vertical segments lie on vertical tracks that span the entire height of the array.

Module Input Connections

The tracks dedicated to module inputs are segmented by pass transistors in each module row. During

normal user operation, the pass transistors are inactive, which isolates the inputs of a module from the

inputs of the module directly above or below it. During certain test modes, the pass transistors are active

to verify the continuity of the metal tracks. Vertical input segments span only the channel above or the

channel below. The logic modules are arranged such that half of the inputs are connected to the channel

above and half of the inputs to segments in the channel below, as shown in Figure 2-9.

Table 2-1 Antifuse Types

Type

Description

XF

Horizontal-to-vertical connection

HF

Horizontal-to-horizontal connection

VF

Vertical-to-vertical connection

FF

"Fast" vertical connection

Figure 2-9

Logic Module Routing Interface

Y+2

Y+1

A1 D10 D11

B1 B0

D01 D00

Y-1

Y-2

LVTs

Y+2

Y+1

Y

Y-1

Y-2

C-Modules

S-Modules

D10

B0

A0 D11 A1

B1 D01

A0

Y

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 211670-4 | CONN D-SUB RCPT 62POS CRIMP |

| 93LC46BX-I/SN | IC EEPROM 1KBIT 2MHZ 8SOIC |

| RMC50DRAS-S734 | CONN EDGECARD 100PS .100 R/A PCB |

| 211668-1 | CONN D-SUB RCPT HSING 26POS HD |

| 93LC46BT/SN | IC EEPROM 1KBIT 2MHZ 8SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A1460A-2PG207C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A1460A-2PQ160C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A1460A-2PQ160I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A1460A-2PQ208C | 制造商: 功能描述: 制造商:undefined 功能描述: |

| A1460A-2PQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。