- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4486 > A42MX09-PL84 (Microsemi SoC)IC FPGA MX SGL CHIP 14K 84-PLCC PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉(h脿o)锛� | A42MX09-PL84 |

| 寤犲晢锛� | Microsemi SoC |

| 鏂囦欢闋�(y猫)鏁�(sh霉)锛� | 117/142闋�(y猫) |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC FPGA MX SGL CHIP 14K 84-PLCC |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 16 |

| 绯诲垪锛� | MX |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 72 |

| 闁€鏁�(sh霉)锛� | 14000 |

| 闆绘簮闆诲锛� | 3 V ~ 3.6 V锛�4.75 V ~ 5.25 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | 0°C ~ 70°C |

| 灏佽/澶栨锛� | 84-LCC锛圝 褰㈠紩绶氾級 |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 84-PLCC锛�29.31x29.31锛� |

绗�1闋�(y猫)绗�2闋�(y猫)绗�3闋�(y猫)绗�4闋�(y猫)绗�5闋�(y猫)绗�6闋�(y猫)绗�7闋�(y猫)绗�8闋�(y猫)绗�9闋�(y猫)绗�10闋�(y猫)绗�11闋�(y猫)绗�12闋�(y猫)绗�13闋�(y猫)绗�14闋�(y猫)绗�15闋�(y猫)绗�16闋�(y猫)绗�17闋�(y猫)绗�18闋�(y猫)绗�19闋�(y猫)绗�20闋�(y猫)绗�21闋�(y猫)绗�22闋�(y猫)绗�23闋�(y猫)绗�24闋�(y猫)绗�25闋�(y猫)绗�26闋�(y猫)绗�27闋�(y猫)绗�28闋�(y猫)绗�29闋�(y猫)绗�30闋�(y猫)绗�31闋�(y猫)绗�32闋�(y猫)绗�33闋�(y猫)绗�34闋�(y猫)绗�35闋�(y猫)绗�36闋�(y猫)绗�37闋�(y猫)绗�38闋�(y猫)绗�39闋�(y猫)绗�40闋�(y猫)绗�41闋�(y猫)绗�42闋�(y猫)绗�43闋�(y猫)绗�44闋�(y猫)绗�45闋�(y猫)绗�46闋�(y猫)绗�47闋�(y猫)绗�48闋�(y猫)绗�49闋�(y猫)绗�50闋�(y猫)绗�51闋�(y猫)绗�52闋�(y猫)绗�53闋�(y猫)绗�54闋�(y猫)绗�55闋�(y猫)绗�56闋�(y猫)绗�57闋�(y猫)绗�58闋�(y猫)绗�59闋�(y猫)绗�60闋�(y猫)绗�61闋�(y猫)绗�62闋�(y猫)绗�63闋�(y猫)绗�64闋�(y猫)绗�65闋�(y猫)绗�66闋�(y猫)绗�67闋�(y猫)绗�68闋�(y猫)绗�69闋�(y猫)绗�70闋�(y猫)绗�71闋�(y猫)绗�72闋�(y猫)绗�73闋�(y猫)绗�74闋�(y猫)绗�75闋�(y猫)绗�76闋�(y猫)绗�77闋�(y猫)绗�78闋�(y猫)绗�79闋�(y猫)绗�80闋�(y猫)绗�81闋�(y猫)绗�82闋�(y猫)绗�83闋�(y猫)绗�84闋�(y猫)绗�85闋�(y猫)绗�86闋�(y猫)绗�87闋�(y猫)绗�88闋�(y猫)绗�89闋�(y猫)绗�90闋�(y猫)绗�91闋�(y猫)绗�92闋�(y猫)绗�93闋�(y猫)绗�94闋�(y猫)绗�95闋�(y猫)绗�96闋�(y猫)绗�97闋�(y猫)绗�98闋�(y猫)绗�99闋�(y猫)绗�100闋�(y猫)绗�101闋�(y猫)绗�102闋�(y猫)绗�103闋�(y猫)绗�104闋�(y猫)绗�105闋�(y猫)绗�106闋�(y猫)绗�107闋�(y猫)绗�108闋�(y猫)绗�109闋�(y猫)绗�110闋�(y猫)绗�111闋�(y猫)绗�112闋�(y猫)绗�113闋�(y猫)绗�114闋�(y猫)绗�115闋�(y猫)绗�116闋�(y猫)鐣�(d膩ng)鍓嶇117闋�(y猫)绗�118闋�(y猫)绗�119闋�(y猫)绗�120闋�(y猫)绗�121闋�(y猫)绗�122闋�(y猫)绗�123闋�(y猫)绗�124闋�(y猫)绗�125闋�(y猫)绗�126闋�(y猫)绗�127闋�(y猫)绗�128闋�(y猫)绗�129闋�(y猫)绗�130闋�(y猫)绗�131闋�(y猫)绗�132闋�(y猫)绗�133闋�(y猫)绗�134闋�(y猫)绗�135闋�(y猫)绗�136闋�(y猫)绗�137闋�(y猫)绗�138闋�(y猫)绗�139闋�(y猫)绗�140闋�(y猫)绗�141闋�(y猫)绗�142闋�(y猫)

40MX and 42MX FPGA Families

1- 72

R e v i sio n 1 1

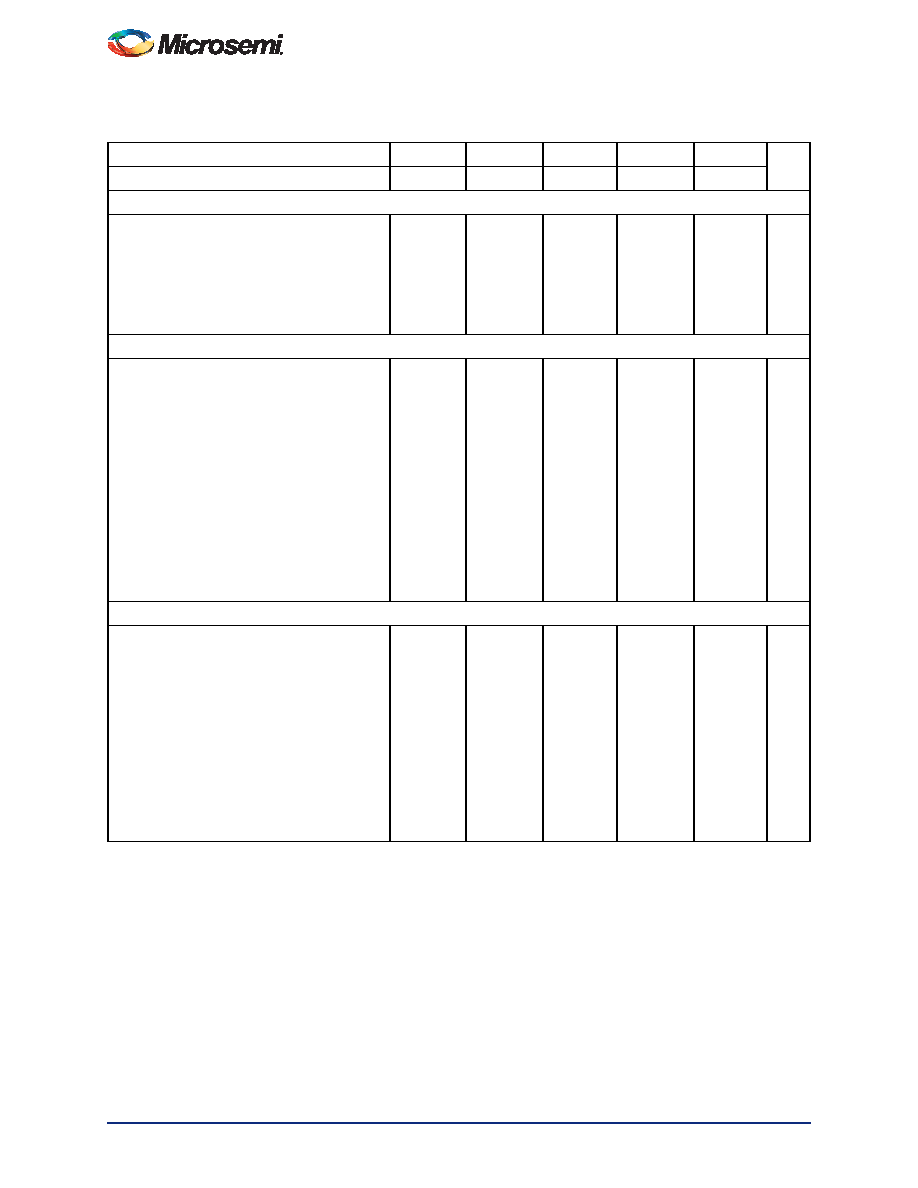

Input Module Predicted Routing Delays2

tIRD1

FO = 1 Routing Delay

2.6

2.9

3.2

3.8

5.3

ns

tIRD2

FO = 2 Routing Delay

2.9

3.2

3.6

4.3

6.0

ns

tIRD3

FO = 3 Routing Delay

3.2

3.6

4.0

4.8

6.6

ns

tIRD4

FO = 4 Routing Delay

3.5

3.9

4.4

5.2

7.3

ns

tIRD8

FO = 8 Routing Delay

4.8

5.3

6.1

7.1

10.0

ns

Global Clock Network

tCKH

Input LOW to HIGH

FO = 32

FO = 486

4.4

4.8

5.3

5.5

6.0

6.5

7.1

9.1

10.0

ns

tCKL

Input HIGH to LOW

FO = 32

FO = 486

5.1

6.0

5.7

6.6

6.4

7.5

7.6

8.8

10.6

12.4

ns

tPWH

Minimum Pulse

Width HIGH

FO = 32

FO = 486

3.0

3.3

3.7

3.8

4.2

4.5

4.9

6.3

6.9

ns

tPWL

Minimum Pulse

Width LOW

FO = 32

FO = 486

3.0

3.3

3.4

3.7

3.8

4.2

4.5

4.9

6.3

6.9

ns

tCKSW

Maximum Skew

FO = 32

FO = 486

0.8

1.0

1.1

1.6

ns

tSUEXT

Input

Latch

External

Set-Up

FO = 32

FO = 486

0.0

ns

TTL Output Module Timing5

tDLH

Data-to-Pad HIGH

3.4

3.8

4.3

5.0

7.1

ns

tDHL

Data-to-Pad LOW

4.0

4.4

5.0

5.9

8.3

ns

tENZH

Enable Pad Z to HIGH

3.6

4.0

4.5

5.3

7.4

ns

tENZL

Enable Pad Z to LOW

3.9

4.4

5.0

5.8

8.2

ns

tENHZ

Enable Pad HIGH to Z

7.2

8.0

9.1

10.7

14.9

ns

tENLZ

Enable Pad LOW to Z

6.7

7.5

8.5

9.9

13.9

ns

tGLH

G-to-Pad HIGH

4.8

5.3

6.0

7.2

10.0

ns

tGHL

G-to-Pad LOW

4.8

5.3

6.0

7.2

10.0

ns

tLSU

I/O Latch Output Set-Up

0.7

0.8

1.0

1.4

ns

Table 1-37 A42MX24 Timing Characteristics (Nominal 3.3 V Operation) (continued)

(Worst-Case Commercial Conditions, VCCA = 3.0 V, TJ = 70掳C)

鈥�3 Speed

鈥�2 Speed

鈥�1 Speed

Std Speed 鈥揊 Speed

Units

Parameter / Description

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

Notes:

1. For dual-module macros, use tPD1 + tRD1 + tPDn, tCO + tRD1 + tPDn, or tPD1 + tRD1 + tSUD, whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for

estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules

can be obtained from the Timer utility.

4. Set-up and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input.

External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an

external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

5. Delays based on 35 pF loading.

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| A42MX16-FPQ208 | IC FPGA MX SGL CHIP 24K 208-PQFP |

| A42MX16-FPQG208 | IC FPGA MX SGL CHIP 24K 208-PQFP |

| A40MX02-2VQG80I | IC FPGA MX SGL CHIP 3K 80-VQFP |

| A40MX02-2VQ80I | IC FPGA MX SGL CHIP 3K 80-VQFP |

| A42MX16-FTQ176 | IC FPGA MX SGL CHIP 24K 176-TQFP |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| A42MX09-PL84A | 鍔熻兘鎻忚堪:IC FPGA MX SGL CHIP 14K 84-PLCC RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:MX 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

| A42MX09-PL84I | 鍔熻兘鎻忚堪:IC FPGA MX SGL CHIP 14K 84-PLCC RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:MX 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

| A42MX09-PL84M | 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:FPGA 14K GATES 336 CELLS 129MHZ/215MHZ 0.45UM 3.3V/5V 84PLCC - Rail/Tube 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:IC FPGA 72 I/O 84PLCC 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:IC FPGA MX SGL CHIP 14K 84-PLCC |

| A42MX09-PLG84 | 鍔熻兘鎻忚堪:IC FPGA 104I/O 84PLCC RoHS:鏄� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:MX 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

| A42MX09-PLG84A | 鍔熻兘鎻忚堪:IC FPGA MX SGL CHIP 14K 84-PLCC RoHS:鏄� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:MX 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

鐧�(f膩)甯冪穵鎬ラ噰璩�(g貌u)锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�