- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1888 > A5303SLETR-T (Allegro Microsystems Inc)IC SMOKE DETECTOR PHOTO 20TSSOP PDF資料下載

參數(shù)資料

| 型號(hào): | A5303SLETR-T |

| 廠商: | Allegro Microsystems Inc |

| 文件頁(yè)數(shù): | 14/15頁(yè) |

| 文件大小: | 0K |

| 描述: | IC SMOKE DETECTOR PHOTO 20TSSOP |

| 特色產(chǎn)品: | A5303 Standard 3V Smoke Detector IC |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 類型: | 煙霧探測(cè)器 |

| 輸入類型: | 光電 |

| 輸出類型: | 電壓 |

| 電流 - 電源: | 300µA |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 20-TSSOP(0.173",4.40mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 20-TSSOP |

| 包裝: | 標(biāo)準(zhǔn)包裝 |

| 其它名稱: | 620-1346-6 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)

Photoelectric Smoke Detector

with Interconnect, Timer, and Latching Alarm Indicator

A5303

8

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

increased by internal selection of C1 so that background reflec-

tions in the smoke chamber can be used to simulate a smoke con-

dition, and IRED pulses every 252 ms (nominal). After the third

IRED pulse (three consecutive simulated smoke conditions), the

successful test signals a continuous passing-test-alarm condition

to the sound IC, outputs the temporal pattern to the piezo horn,

and activates the I/O pin. When the pushbutton is released, the

input returns to VSS due to the internal pulldown. After one oscil-

lator cycle, the amplifier gain returns to normal, and after three

additional IRED pulses (less than one second), the device exits

this mode and returns to standby. This high-to-low transition on

TEST also resets and starts the 10-minute (nominal) “hush” timer

mode, if the mode is enabled via the HUSH pin. The high-to-low

transition also resets the latching alarm indicator, if it is latched.

If the chamber malfunctions or is too dirty, the push-test will fail

to simulate a smoke condition, and after three failed STROBE

pulses the device signals a continuous failing-test-alarm condi-

tion on the SOUTx pins. The piezo driver and the I/O pins are not

enabled.

Diagnostic Test/Calibration mode is available to facilitate calibra-

tion and test of the IC and the assembled detector. It is initiated

by pulling TEST below VSS by continuously drawing 200 μA

from the pin for at least one clock cycle on OSC CAP. The cur-

rent should not exceed 500 μA and under these conditions,

TEST pin voltage will clamp at approximately 250 mV below

VSS. One option is to connect TEST to a –5 V supply through a

15 kΩ resistor. In this mode, certain device pins are reconfigured

as described in table 1. The IRED pulse rate is increased to one

pulse every OSC CAP cycle and the STROBE pin is always

active. To exit this mode, the TEST pin should be floated, or

returned to VSS, for at least one OSC CAP cycle.

Latching Alarm Indicator

When multiple smoke detectors are networked through the I/O

line, the latching alarm indicator allows the user to identify which

detector(s) initiated an alarm. When a local alarm condition

occurs, the initiating detector(s) will latch the event in memory.

After the alarm condition has expired (the device stops signaling

the alarm condition to the sound IC) the initiating detector(s) will

output an additional 10 ms LED pulse every 43 seconds. If the

BLINK pin is connected to VDD, the additional pulse will occur

0.67 seconds after the normal standby pulse. The user can clear

the latched alarm condition by pressing and releasing the push-to-

test button. If the user does not press the push-to-test button, the

latched alarm condition will cease after 24 hours to preserve bat-

tery life, and to prevent masking future latched alarm indications.

Alarm Indications

Alarm conditions include: local smoke detection, a remote alarm,

low battery, and degraded chamber sensitivity. These are indi-

cated by a combination of SOUTx output, piezo horn, and LED

signals, which continue until the alarm condition is resolved.

A local alarm always overrides a remote alarm and a push-test.

Remote alarm always overrides a push-test. A local alarm, remote

alarm, or a push-test will inhibit warning signals for low battery

or degraded chamber.

During a local or a remote alarm condition, the device continu-

ously signals an alarm condition on the SOUTx pins that indi-

cates the type of the alarm. The piezo horn output is a continuous

modulated tone (temporal horn pattern), nominally: 0.5 s on, 0.5 s

off, 0.5 s on, 0.5 s off, 0.5 s on, and 1.5 s off. The visible LED

also distinguishes a local alarm from a remote alarm. During a

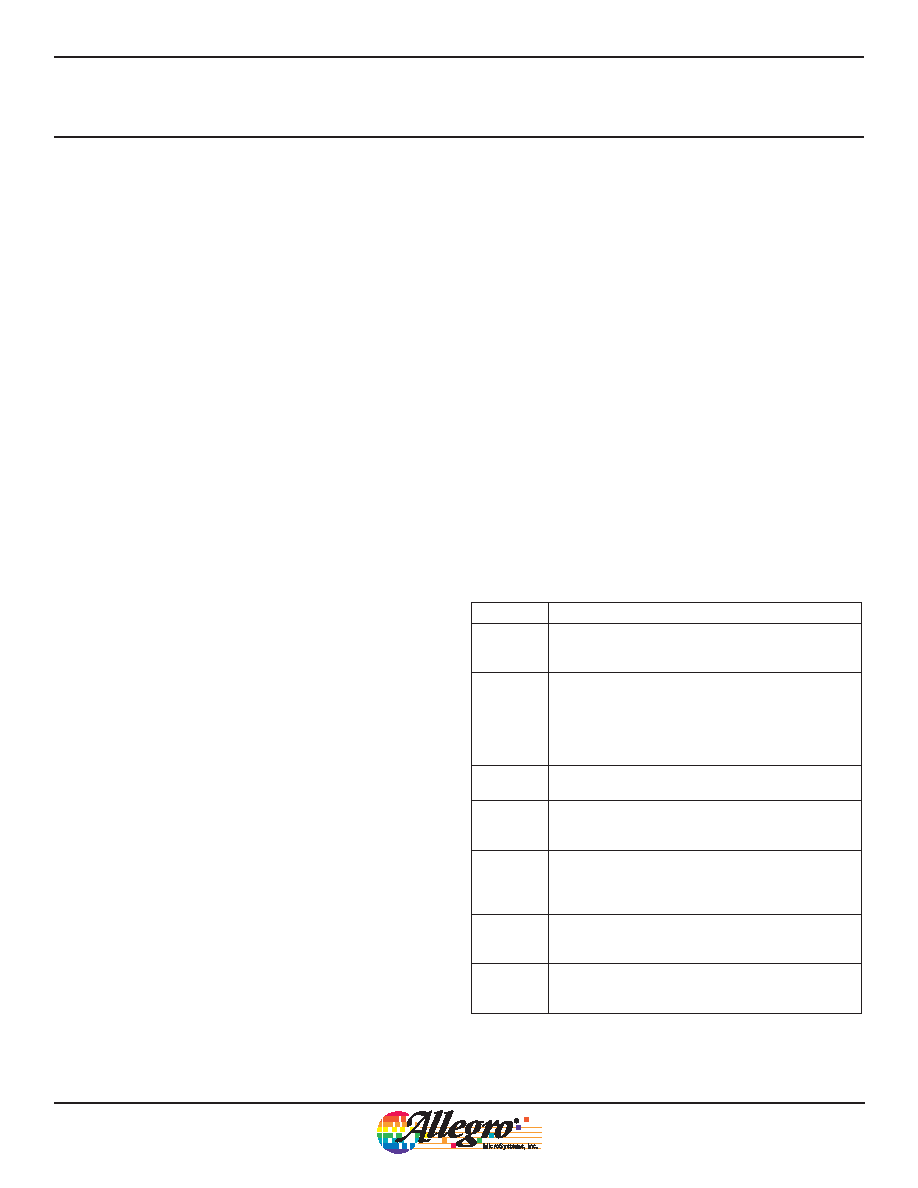

Table 1. Alternate Pin Configuration During Diagnostic

Test/Calibration Mode

Pin Name

Alternate Configuration

I/O

Disabled as an output. A logic high on this pin places the

photoamplifier output on the BLINK pin. The amplifier

output appears as pulses.

HUSH

If the I/O pin is high, this pin controls the amplifier gain

capacitor. If this pin is low, normal gain is selected. If this

pin is high, supervisory gain is selected.

NOTE: If I/O is low, clocking this pin will cause the

device to exit diagnostic/calibration mode and enter an

Allegro-defined test mode.

BLINK

If the I/O pin is high, this pin is reconfigured as the

photoamplifier output.

SOUT0

If the I/O pin is high and the HUSH pin is low (normal

gain), taking this pin to a high logic level increases the

amplifier gain by ≈45% (hysteresis).

SOUT2

This pin is reconfigured as the smoke integrator output.

Three consecutive smoke detections will cause this pin

to go high and three consecutive no-smoke detections

cause this pin to go low.

LED

This pin becomes a low-battery indicator. The open-

drain NMOS output is normally off. If VDD falls below the

low-battery threshold, the output turns on.

OSC CAP

This pin may be driven by an external clock source.

Driving this pin low and high drives the internal clock low

and high. The external RC network may remain intact.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A5348CA-T | IC SMOKE DETECTOR ION 16-DIP |

| A5350CA-T | IC SMOKE DETECTOR ION 16-DIP |

| A5358CLWTR-T | IC SMOKE DETECTOR PHOTO 16-SOIC |

| A5366CLWTR-T | IC SMOKE DETECTOR PHOTO 16-SOIC |

| A5367CA-T | IC SMOKE DETECTOR ION 16-DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A5309C1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| A5309C2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| A5309C3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| A5309C4 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| A5309C5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。