- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366309 > A8237 (Altera Corporation) PROGRAMMABLE DMA CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | A8237 |

| 廠商: | Altera Corporation |

| 英文描述: | PROGRAMMABLE DMA CONTROLLER |

| 中文描述: | 可編程DMA控制器 |

| 文件頁數(shù): | 2/22頁 |

| 文件大?。?/td> | 269K |

| 代理商: | A8237 |

6

Altera Corporation

a8237 Programmable DMA Controller Data Sheet

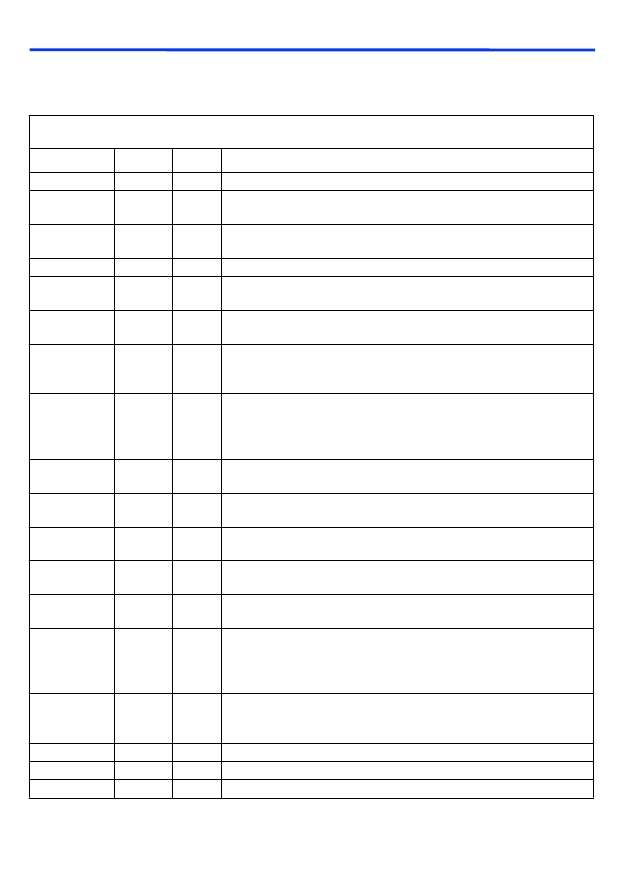

Table 1

describes the input and output ports of the

a8237

MegaCore

function.

Table 1. a8237 Ports (Part 1 of 2)

Name

Type

Polarity

Description

clk

Input

Input

–

Clock. Used to generate and synchronize

a8237

operations.

Hold acknowledge. This signal from the microprocessor indicates the

release of the system bus to the

a8237

.

Chip select. When

ncs

is active, the

a8237

is selected, and read and

write transactions to internal registers are enabled.

End of process. Permits external termination of the current DMA service.

I/O read control. When

niorin

is low and the

a8237

is selected, read

transactions from internal registers are enabled.

I/O write control. When

niowin

is low and the

a8237

is selected, data is

asynchronously written into the

a8237

.

Ready. Extends the read and write pulses associated with slow memory

or peripherals. When

ready

is low, wait states are inserted until

ready

returns high.

Reset. Clears the command, status, request, and temporary registers.

Also clears the byte pointer, mode register counter, and the controller

state machine. Sets the mask register so requests are ignored after

initialization.

Register address bus. Selects one of the internal

a8237

registers. See

Table 2 on page 9

.

Data bus input. The microprocessor writes data to internal registers via

the

dbin[7..0]

bus.

DMA request bus. Programmable polarity. Asynchronous signals from

peripherals requesting DMA service.

Address strobe. Latches the MSB of the DMA address from

dbout[7..0]

into an external address latch.

Address enable. Enables an external address latch containing the most

significant address byte of a DMA transfer.

Data bus enable. Active when data registers are read. Also active during

DMA transfers, allowing the most significant bit (MSB) of the address to

latch the output of temporary register data during memory-to-memory

writes.

DMA enable. Asserted during an active DMA cycle. Can create

bidirectional signals from the

niorin

,

niorout

,

niowin

, and

niowout

signals, and the lower four bits of the address bus.

Hold request. Requests control of the system bus.

End of process. Indicates normal termination of a DMA transfer.

I/O read output. Read strobe to I/O devices as DMA writes to memory.

hlda

High

ncs

Input

Low

neopin

Input

Input

Low

Low

niorin

niowin

Input

Low

ready

Input

High

reset

Input

High

ain[3..0]

Input

–

dbin[7..0]

Input

–

dreq[3..0]

Input

–

adstb

Output

High

aen

Output

High

dben

Output

High

dmaenable

Output

High

hrq

Output

Output

Output

High

Low

Low

neopout

niorout

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| a8251 | Programmable Communications Interface(可編程通信接口) |

| a8255 | Programmable Peripheral Interface Adapter(可編程外圍接口適配器) |

| A8255 | PROGRAMMABLE PERIPHERAL INTERFACE ADAPTER |

| a8259 | Programmable Interrupt Controller(可編程中斷控制器) |

| A8406-53 | Various types of cables for frame grabber |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A82370-16 | 制造商:Rochester Electronics LLC 功能描述: |

| A82380-16 | 制造商:Intel 功能描述:PERIPHERAL (MULTIFUNCTION) CONTROLLER, 132 Pin, PGA |

| A82380-20 | 制造商:Rochester Electronics LLC 功能描述: |

| A82380-25 | 制造商:Rochester Electronics LLC 功能描述: |

| A82385-16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Cache Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。