- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6640AST (ANALOG DEVICES INC) 12-Bit, 65 MSPS IF Sampling A/D Converter PDF資料下載

參數(shù)資料

| 型號: | AD6640AST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| 中文描述: | 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP44 |

| 封裝: | PLASTIC, MS-026BCB, LQFP-44 |

| 文件頁數(shù): | 19/24頁 |

| 文件大?。?/td> | 488K |

| 代理商: | AD6640AST |

AD6640

REV. 0

–19–

System Requirements

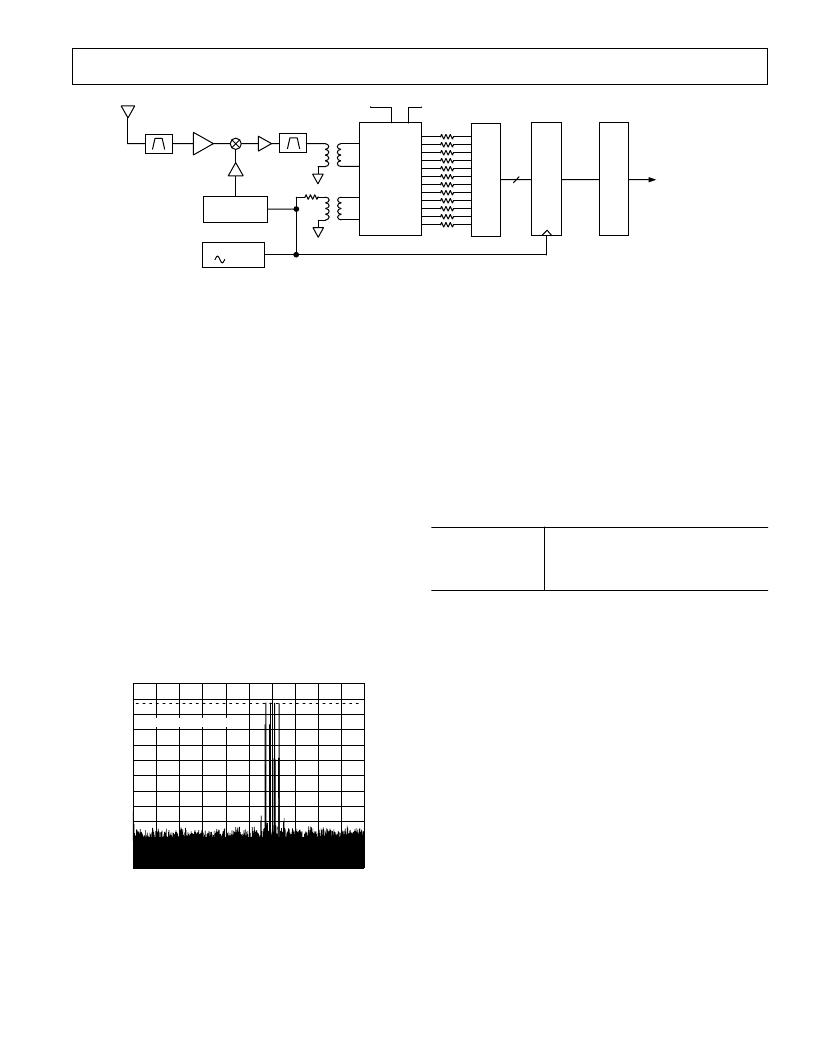

Figure 46 shows a typical wideband receiver subsystem based

around the AD6640. T his strip consists of a wideband IF filter,

amplifier, ADC, latches, channelizer and interface to a digital

signal processor. T his design shows a typical clocking scheme

used in many receiver designs. All timing within the system is

referenced back to a single clock. While this is not necessary, it

does facilitate PLL design, ease of manufacturing, system test,

and calibration. K eeping in mind that the overall performance

goal is to maintain the best possible dynamic range, many con-

siderations must be made.

One of the biggest challenges is selecting the amplifier used to

drive the AD6640. Since this is a communications application,

it is common to directly sample an intermediate frequency (IF)

signal. As such, IF gain blocks can be implemented instead of

baseband op amps. For these gain block amplifiers, the critical

specifications are third order intercept point and noise figure. A

bandpass filter will remove harmonics generated within the

amplifier, but intermods should be better than the performance

of the A/D converter. In the case of the AD6640, amplifier

intermods must be better than –80 dBFS when driving full-

scale power. As mentioned earlier, there are several amplifiers

to choose from and the specifications depend on the end

application. Figure 47 shows a typical multitone test.

FREQUENCY – MHz

0

–80

–120

–40

–100

–20

–60

dc

32.5

6.5

P

13.0

19.5

26.0

ENCODE = 65MSPS

Figure 47. Multitone Performance

T wo other key considerations for the digital wideband receiver

are converter sample rate and IF frequency range. Since per-

formance of the AD6640 converter is largely independent of

both sample rate and analog input frequency (Figures 10, 11

and 16), the designer has greater flexibility in the selection of

these parameters. Also, since the AD6640 is a bipolar device,

power dissipation is not a function of sample rate. T hus there is

no penalty paid in power by operating at faster sample rates. All

of this is good because, by carefully selecting input frequency

range and sample rate, some of the drive amplifier and ADC

harmonics can actually be placed out-of-band.

For example, if the system has second and third harmonics that

are unacceptably high, by carefully selecting the encode rate and

signal bandwidth, these second and third harmonics can be

placed out-of-band. For the case of an encode rate equal to

60 MSPS and a signal bandwidth of 7.5 MHz, placing the fun-

damental at 7.5 MHz places the second and third harmonics out

of band as shown in the table below.

T able II.

Encode Rate

Fundamental

Second Harmonic

T hird Harmonic

60 MSPS

7.5 MHz–15 MHz

15 MHz–30 MHz

22.5 MHz–30 MHz, 30 MHz–15 MHz

Another option can be found through bandpass sampling. If the

analog input signal range is from dc to FS/2, then the amplifier

and filter combination must perform to the specification re-

quired. However, if the signal is placed in the third Nyquist

zone (FS to 3 FS/2), the amplifier is no longer required to meet

the harmonic performance required by the system specifications

since all harmonics would fall outside the passband filter. For

example, the passband filter would range from FS to 3 FS/2.

T he second harmonic would span from 2 FS to 3 FS, well out-

side the passband filter’s range. T he burden then has been passed

off to the filter design provided that the ADC meets the basic

specifications at the frequency of interest. In many applications,

this is a worthwhile tradeoff since many complex filters can

easily be realized using SAW and LCR techniques alike at these

relatively high IF frequencies. Although harmonic performance

of the drive amplifier is relaxed by this technique, intermodula-

tion performance cannot be sacrificed since intermods must be

assumed to fall in-band for both amplifiers and converters.

Noise Floor and SNR

Oversampling is sampling at a rate that is greater than twice the

bandwidth of the signal desired. Oversampling does not have

anything to do with the actual frequency of the sampled sig-

nal, it is the bandwidth of the signal that is key. Bandpass or

“IF” sampling refers to sampling a frequency that is higher than

Nyquist and often provides additional benefits such as down

conversion using the ADC and replacing a mixer with a track-

and-hold. Oversampling leads to processing gains because the

PRESELECT

FILTER

LNA

5–15MHz

PASSBAND

348

V

CMOS

BUFFER

D11

D0

+3.3V (D)

+5V (A)

AD6640

AIN

ENCODE

ENCODE

M/N PLL

SYNTHESIZER

LO

DRIVE

REF

IN

1900MHz

REFERENCE

CLOCK

65.00MHz

12

AD6620

(REF. FIG 45)

I & Q

DATA

CLK

ADSP-2181

NETWORK

CONTROLLER

INTERFACE

AIN

Figure 46. Simplified Wideband PCS Receiver

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6640PCB | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640ST | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6644 | 14-Bit, 40 MSPS/65 MSPS A/D Converter |

| AD6644PCB | 14-Bit, 40 MSPS/65 MSPS A/D Converter |

| AD6644ST | 14-Bit, 40 MSPS/65 MSPS A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6640ASTZ | 功能描述:IC ADC 12BIT 65MSPS 44-LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 其它 IC 和模塊 系列:- 標(biāo)準(zhǔn)包裝:100 系列:* |

| AD6640PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640ST | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640ST/PCB | 制造商:Analog Devices 功能描述: |

| AD6641 | 制造商:AD 制造商全稱:Analog Devices 功能描述:250 MHz Bandwidth DPD Observation Receiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。