- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6655BCPZ-1501 (Analog Devices, Inc.) IF Diversity Receiver PDF資料下載

參數(shù)資料

| 型號: | AD6655BCPZ-1501 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | IF Diversity Receiver |

| 中文描述: | IF分集接收機(jī) |

| 文件頁數(shù): | 53/84頁 |

| 文件大?。?/td> | 2012K |

| 代理商: | AD6655BCPZ-1501 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當(dāng)前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

AD6655

Rev. 0 | Page 53 of 84

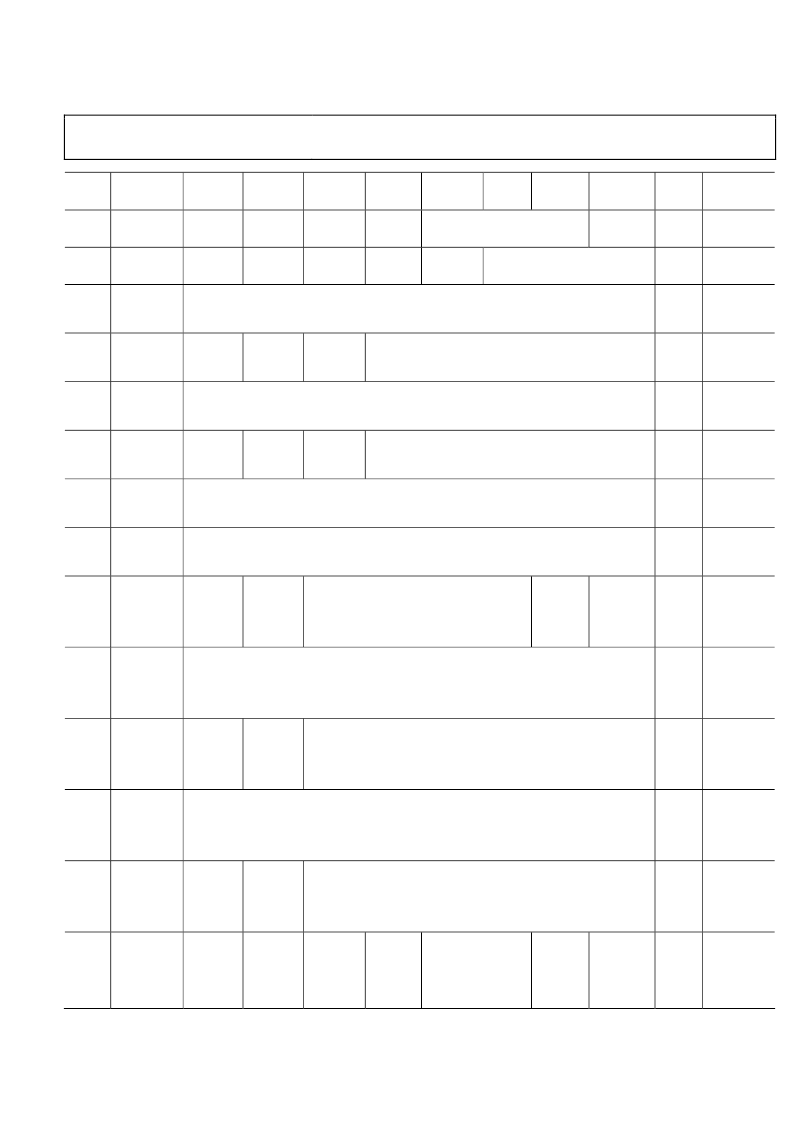

Addr.

(Hex)

0x104

Register

Name

Fast Detect

Control

(Local)

Coarse Upper

Threshold

(Local)

Fine Upper

Threshold

Register 0

(Local)

Fine Upper

Threshold

Register 1

(Local)

Fine Lower

Threshold

Register 0

(Local)

Fine Lower

Threshold

Register 1

(Local)

Increase Gain

Dwell Time

Register 0

(Local)

Increase Gain

Dwell Time

Register 1

(Local)

Signal

Monitor

DC

Correction

Control

(Global)

Signal

Monitor

DC Value

Channel A

Register 0

(Global)

Signal

Monitor

DC Value

Channel A

Register 1

(Global)

Signal

Monitor

DC Value

Channel B

Register 0

(Global)

Signal

Monitor

DC Value

Channel B

Register 1

(Global)

Signal

Monitor

SPORT

Control

(Global)

Bit 7

(MSB)

Open

Bit 6

Open

Bit 5

Open

Bit 4

Open

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Fast detect

enable

Default

Value

(Hex)

0x00

Default

Notes/

Comments

Fast Detect Mode Select[2:0]

0x105

Open

Open

Open

Open

Open

Coarse Upper Threshold[2:0]

0x00

0x106

Fine Upper Threshold[7:0]

0x00

0x107

Open

Open

Open

Fine Upper Threshold[12:8]

0x00

0x108

Fine Lower Threshold[7:0]

0x00

0x109

Open

Open

Open

Fine Lower Threshold[12:8]

0x00

0x10A

Increase Gain Dwell Time[7:0]

0x00

In ADC clock

cycles

0x10B

Increase Gain Dwell Time[15:8]

0x00

In ADC clock

cycles

0x10C

Open

DC

correction

freeze

DC Correction Bandwidth(k:[3:0])

DC

correction

for signal

path

enable

DC

correction

for signal

monitor

enable

0x00

0x10D

DC Value Channel A[7:0]

Read only

0x10E

Open

Open

DC Value Channel A[13:8]

Read only

0x10F

DC Value Channel B[7:0]

Read only

0x110

Open

Open

DC Value Channel B[13:8]

Read only

0x111

Open

RMS

magnitude

output

enable

Peak

detector

output

enable

Threshold

crossing

output

enable

SPORT SMI SCLK

divide

00 = Undefined

01 = divide by 2

10 = divide by 4

11 = divide by 8

SPORT

SMI SCLK

sleep

Signal

monitor

SPORT

output

enable

0x04

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6655BCPZ-801 | IF Diversity Receiver |

| AD667JN | Microprocessor-Compatible 12-Bit D/A Converter |

| AD667JP | Microprocessor-Compatible 12-Bit D/A Converter |

| AD667KN | Microprocessor-Compatible 12-Bit D/A Converter |

| AD667KP | Microprocessor-Compatible 12-Bit D/A Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6655BCPZ-80 | 制造商:Analog Devices 功能描述:IF Diversity Receiver 64-Pin LFCSP EP 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 |

| AD6655BCPZ-80 | 制造商:Analog Devices 功能描述:Communication IC |

| AD6655BCPZ-801 | 制造商:AD 制造商全稱:Analog Devices 功能描述:IF Diversity Receiver |

| AD6655BCPZRL7-125 | 制造商:Analog Devices 功能描述: |

| AD6655BCPZRL7-150 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。