- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄17065 > AD9788-DPG2-EBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9788 PDF資料下載

參數(shù)資料

| 型號(hào): | AD9788-DPG2-EBZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 20/64頁 |

| 文件大?。?/td> | 0K |

| 描述: | BOARD EVALUATION FOR AD9788 |

| 設(shè)計(jì)資源: | Powering the AD9788 Using ADP2105 for Increased Efficiency (CN0141) |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

| DAC 的數(shù)量: | 2 |

| 位數(shù): | 16 |

| 采樣率(每秒): | 800M |

| 數(shù)據(jù)接口: | 串行 |

| 設(shè)置時(shí)間: | 22ms |

| DAC 型: | 電流 |

| 工作溫度: | -40°C ~ 85°C |

| 已供物品: | * |

| 已用 IC / 零件: | AD9788 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

AD9785/AD9787/AD9788

Rev. A | Page 27 of 64

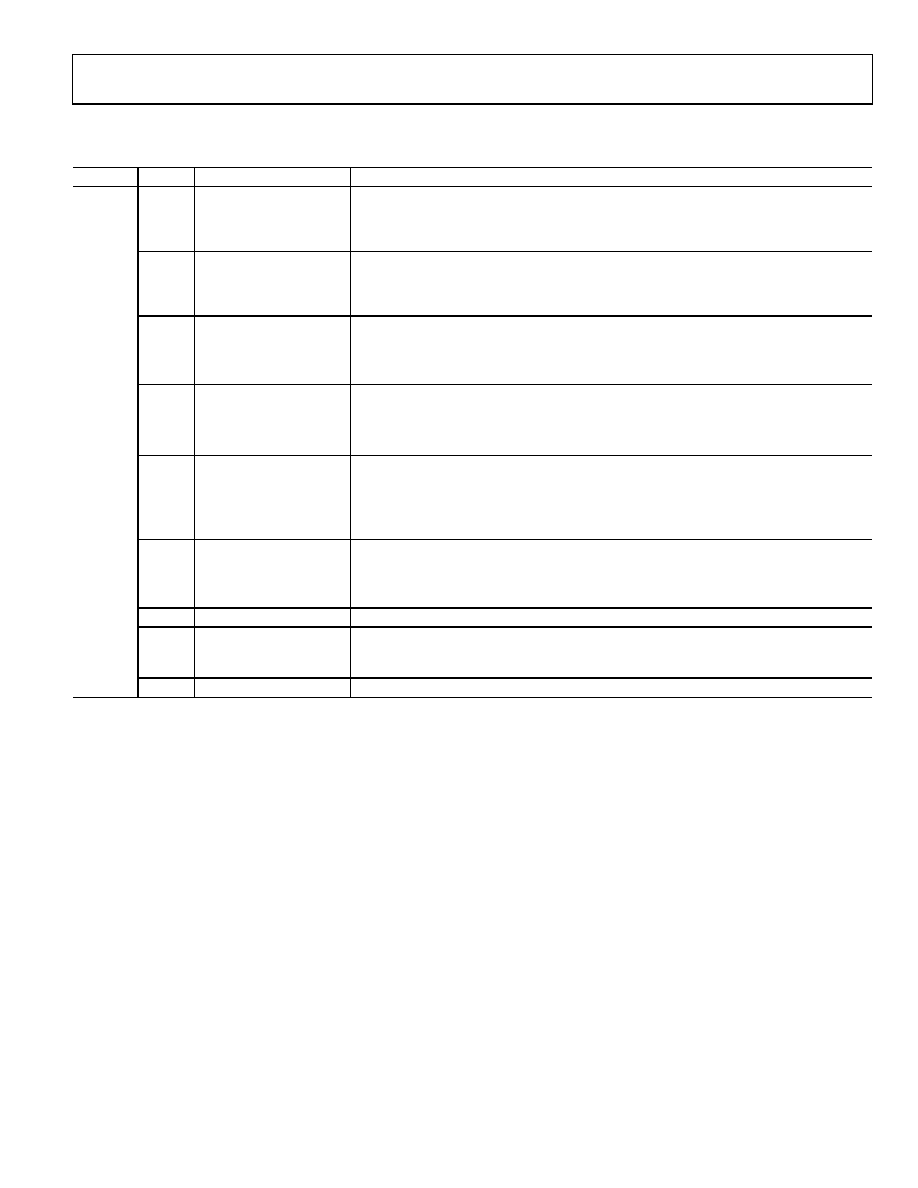

The data synchronization control register (DSCR) comprises two bytes located at Address 0x02.

Table 12. Data Synchronization Control Register (DSCR)

Address

Bit

Name

Description

0x02

[15:11]

DATACLK Delay [4:0]

Controls the amount of delay applied to the output data clock signal. The minimum delay

corresponds to the 00000 state, and the maximum delay corresponds to the 11111 state.

The minimum delay is 0.7 ns and the maximum delay is 6.5 ns. The incremental delay is

190 ps and corresponds to an incremental change in the data clock delay bits.

[10:7]

Data Timing Margin [3:0]

The data timing margin bits control the amount of delay applied to the data and clock

signals used for checking setup and hold times, respectively, on the input data ports, with

respect to the internal data assembler clock. The minimum delay corresponds to the 0000

state, and the maximum delay corresponds to the 1111 state. The delays are 190 ps.

[6]

LVDS data clock enable

0: Default. When the LVDS data clock enable bit is cleared, the SYNC_O+ and SYNC_O

LVDS pad cells are driven by the multichip synchronization logic.

1: When the LVDS data clock enable bit is set, the SYNC_O+ and SYNC_O LVDS pad cells

are driven by the signal that drives the CMOS DATACLK output pad.

[5]

DATACLK invert

0: Default. When the data clock invert bit is cleared, the DATACLK signal is in phase with

the clock that samples the data into the part.

1: When the DATACLK invert bit is set, the DATACLK signal is inverted from the clock that

samples the data into the part.

[4]

DATACLK delay enable

0: Default. When the DATACLK delay enable bit is cleared, the data port input

synchronization function is effectively inactive and the delay is bypassed.

1: When the DATACLK delay enable bit is set, the data port input synchronization function

is active and controlled by the data delay mode bits. The data output clock is routed

through the delay cell.

[3]

Data timing mode

Determines the timing optimization mode. See the Optimizing the Data Input Timing

section for details.

0: Manual timing optimization mode

1: Automatic timing optimization mode

[2]

Set high

This bit should always be set high.

[1]

Data sync polarity

0: Default. The digital input data sampling edge is aligned with the falling edge of DCI.

1: The digital input data sampling edge is aligned with the rising edge of DCI.

Used only in slave mode (see the MSCR register, Address 0x03, Bit 16).

[0]

Reserved

Reserved for future use.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SLPX223M025E7P3 | CAP ALUM 22000UF 25V 20% SNAP |

| EMA10DTKS | CONN EDGECARD 20POS DIP .125 SLD |

| EVAL-AD5392EBZ | BOARD EVAL FOR AD5392 |

| 380LX682M025H022 | CAP ALUM 6800UF 25V 20% SNAP |

| DC941A | BOARD DELTA SIGMA ADC LTC2482 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9788-EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD9788 制造商:Analog Devices 功能描述:DUAL 16B, D-A CONVERTER - Bulk 制造商:Analog Devices 功能描述:Digital to Analog Eval. Board |

| AD9788MOD-EBZ | 制造商:Analog Devices 功能描述:DUAL 12-/14-/16-BIT 800 MSPS DAC WITH LOW POWER 32-BIT COMPLEX NCO 制造商:Analog Devices 功能描述:DUAL 16B, D-A CONVERTER - Bulk |

| AD9789BBC | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 14 Bit 2.5 GSPS D-A Converter RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| AD9789BBCRL | 制造商:Analog Devices 功能描述:QAM Encoder/Interpolator/Upconverter 164-Pin CSP-BGA T/R 制造商:Analog Devices 功能描述:QAM ENCODER/INTERPOLATOR/UPCNVRTR 164CSPBGA - Tape and Reel 制造商:Analog Devices 功能描述:IC DAC 14BIT 2.4GSPS 4CH 164BGA 制造商:Analog Devices Inc. 功能描述:Digital to Analog Converters - DAC 14 Bit 2.5 GSPS D-A Converter 制造商:Analog Devices Inc. 功能描述:Digital to Analog Converters - DAC 14B 2400MSPS RF w/ 4CH Signal Process 制造商:Analog Devices 功能描述:CONVERTER - DAC |

| AD9789BBCZ | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 14 Bit 2.5 GSPS D-A Converter RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。