- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379645 > ADM7008 (Electronic Theatre Controls, Inc.) Octal Ethernet 10/100M PHY PDF資料下載

參數(shù)資料

| 型號(hào): | ADM7008 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Octal Ethernet 10/100M PHY |

| 中文描述: | 八路個(gè)10/100M以太網(wǎng)物理層 |

| 文件頁(yè)數(shù): | 18/92頁(yè) |

| 文件大小: | 981K |

| 代理商: | ADM7008 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

ADM7008

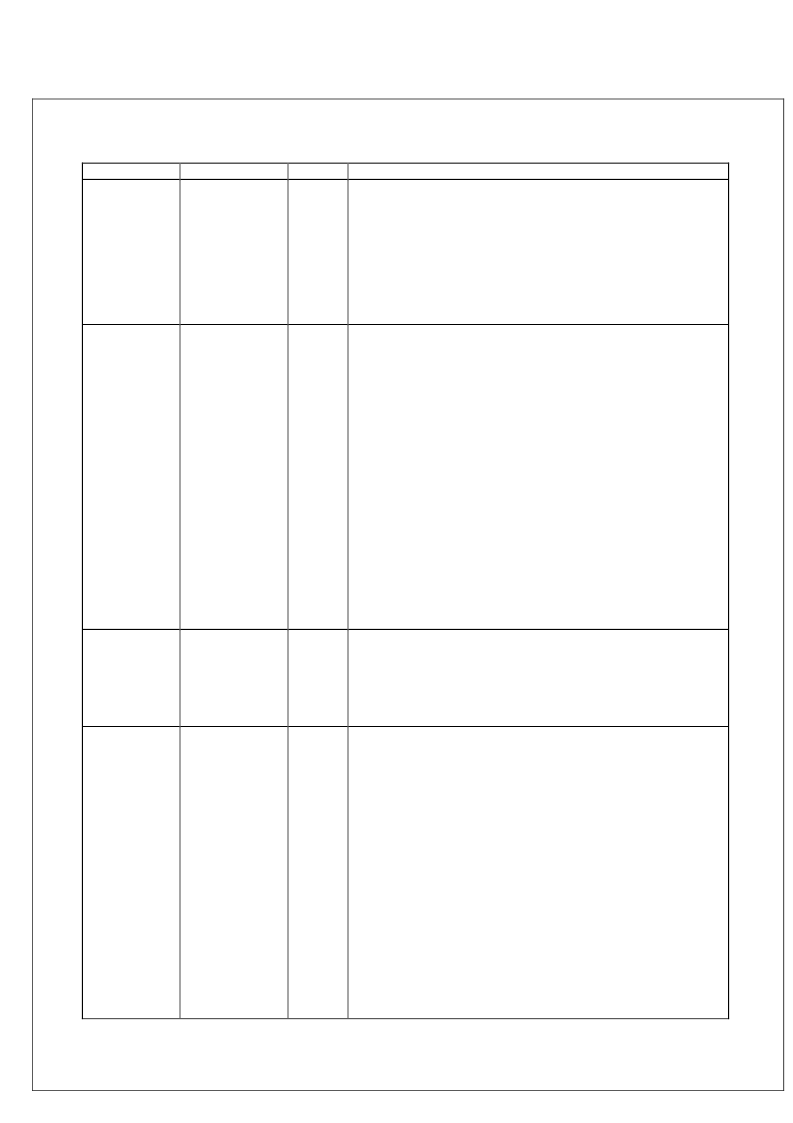

Interface Description

Pin #

Pin Name

Type

Pin Description

CRSDV_P6 is asserted synchronously to REFCLK. The

toggling of CRSDV_P6 on the first and second di-bit continues

until all the data in the FIFO is presented onto RXD.

CRSDV_P6 is asserted for the duration of carrier activity for a

false carrier event.

Not Used.

Not used in SMII/SS_SMII Mode

Port 6 RMII Transmit Data. Transmit data for port 6 input the

di-bits that re transmitted and are driven synchronously to

REFCLK. Note that in 100Mb/s mode, TXD can change once

per REFCLK cycle, whereas in 10Mb/s mode, TXD must be

held steady for 10 consecutive REFCLK cycles.

Link and Activity LED/Port 6 SMII Transmit Data. TXD0 for port

6 inputs the data that is transmitted and is driven synchronously

to SMII_REFCLK (pin 70). In 100Mb/s mode, TXD0 inputs a

new 10-bit segment starting with SYNC. In 10Mb/s mode,

TXD0 must repeat each 10-bit segment 10 times.

TXD1_P6 acts as Port 6 Link/Activity LED in both SMII and

SS_SMII Mode. See LED Description for more detail.

Link and Activity LED/Port 6 SS_SMII Transmit Data. TXD0 for

port 6 inputs the data that is transmitted and is driven

synchronously to TXCLK (pin 70). In 100Mb/s mode, TXD0

inputs a new 10-bit segment starting with SYNC. In 10Mb/s

mode, TXD0 must repeat each 10-bit segment 10 times.

Port 6 Transmit Enable. Transmit Enable for port 6 indicates

that the di-bit on TXD is valid and it is driven synchronously to

REFCLK.

TIED TO LOW. TXEN_P6 should be tied to low for normal

operation in both SMII and SS_SMII Mode.

REC_10M: Value on RXD1_P5 will be latched by ADM7008

during power on reset as Port 5 10M Re-command value.

0: Recommend Port 5 to operate in 100M Mode (Default)

1: Recommend Port 5 to operate in 10M Mode

Lower power Link Pulse Function (Power Saving, LLP) Disable.

Value on RXD1 will be latched by ADM7008 during power on

reset as power saving disable signal. (See Lower Power Link

Pulse Function description for more detail)

0: Power Saving Enable

1: Power Saving disable (Default)

Port 5 RMII Receive Data. RXD[1:0] are the port 5 output di-

bits synchronously to REFCLK. Upon assertion of CRSDV_P,

RXD0 and RXD1 remain at 00 until valid data is output from the

FIFO onto RXD. 01 on RXD1 and RXD0 indicates the start of

valid data. If a false carrier or a symbol error is detected, RXD1

and RXD0 are set to 10 for the duration of the activity. Note

that in 100Mb/s mode RXD can change once per REFCLK

ADMtek Inc.

2-6

SMII/SS_SMII

Mode

N/A

62, 63

RMII Mode

TXD[1:0]_P6

SMII Mode

LNKACT_P6,

SMII_TXD_P6

SS_SMII Mode

LNKACT_P6,

SSSMII_TXD_P6

I,

LVTTL,

PD,

PD

64

RMII Mode

TXEN_P6

SMII/SS_SMII

LOW

Power On

Setting

REC_10M_P5,

PWSAVE_DIS

RMII Mode

RXD[1:0]_P5

I,

TTL

65, 66

I,

PD,

PD

O,

8mA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADM9511 | LAN/Modem Controller with Embedded Fast Ethernet PHY |

| ADS-238Q | 12-Bit, 20MHz, Low Power Sampling A/D Converters |

| ADS-917GC | 14-Bit, 1MHz, Low-Power Sampling A/D Converters |

| ADS-927GC | 14-Bit, 1MHz, Low-Power Sampling A/D Converters |

| ADS-927GM | 14-Bit, 1MHz, Low-Power Sampling A/D Converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADM7008A3T1 | 功能描述:IC SWITCH CTRLR 10/100 128PQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類(lèi)型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| ADM7008A3T1NP | 制造商:Infineon Technologies AG 功能描述:SWITCH / PHY |

| ADM7008XA3T1 | 功能描述:IC SWITCH CTRLR 10/100 128PQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類(lèi)型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| adm7008x-a3-t-1 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Infineon Technologies AG 功能描述: |

| ADM7008XA3T1XP | 制造商:Infineon Technologies AG 功能描述:GREEN, SWITCH / PHY |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。