- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4408 > AGLE600V5-FG484I (Microsemi SoC)IC FPGA 1KB FLASH 600K 484-FBGA PDF資料下載

參數(shù)資料

| 型號: | AGLE600V5-FG484I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 1/166頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1KB FLASH 600K 484-FBGA |

| 標準包裝: | 60 |

| 系列: | IGLOOe |

| 邏輯元件/單元數(shù): | 13824 |

| RAM 位總計: | 110592 |

| 輸入/輸出數(shù): | 270 |

| 門數(shù): | 600000 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 484-BGA |

| 供應商設備封裝: | 484-FPBGA(23x23) |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

December 2012

I

2012 Microsemi Corporation

IGLOOe Low Power Flash FPGAs

with Flash*Freeze Technology

Features and Benefits

Low Power

1.2 V to 1.5 V Core Voltage Support for Low Power

Supports Single-Voltage System Operation

Low-Power Active FPGA Operation

Flash*Freeze

Technology

Enables

Ultra-Low

Power

Consumption while Maintaining FPGA Content

Flash*Freeze Pin Allows Easy Entry to / Exit from Ultra-Low-

Power Flash*Freeze Mode

High Capacity

600 k to 3 Million System Gates

108 to 504 kbits of True Dual-Port SRAM

Up to 620 User I/Os

Reprogrammable Flash Technology

130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOS

Process

Instant On Level 0 Support

Single-Chip Solution

Retains Programmed Design when Powered Off

250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System

Performance

In-System Programming (ISP) and Security

ISP Using On-Chip 128-Bit Advanced Encryption Standard

(AES) Decryption via JTAG (IEEE 1532–compliant)

FlashLock Designed to Secure FPGA Contents

High-Performance Routing Hierarchy

Segmented, Hierarchical Routing and Clock Structure

High-Performance, Low-Skew Global Network

Architecture Supports Ultra-High Utilization

Pro (Professional) I/O

700 Mbps DDR, LVDS-Capable I/Os

1.2

V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation

Bank-Selectable I/O Voltages—Up to 8 Banks per Chip

Single-Ended I/O Standards: LVTTL, LVCMOS 3.3 V /

2.5 V / 1.8 V / 1.5 V / 1.2 V, 3.3 V PCI / 3.3 V PCI-X, and

LVCMOS 2.5 V / 5.0 V Input

Differential I/O Standards: LVPECL, LVDS, B-LVDS, and

M-LVDS

Voltage-Referenced I/O Standards: GTL+ 2.5 V / 3.3 V, GTL

2.5 V / 3.3 V, HSTL Class I and II, SSTL2 Class I and II, SSTL3

Class I and II

Wide Range Power Supply Voltage Support per JESD8-B,

Allowing I/Os to Operate from 2.7 V to 3.6 V

Wide Range Power Supply Voltage Support per JESD8-12,

Allowing I/Os to Operate from 1.14 V to 1.575 V

I/O Registers on Input, Output, and Enable Paths

Hot-Swappable and Cold-Sparing I/Os

Programmable Output Slew Rate and Drive Strength

Programmable Input Delay

Schmitt Trigger Option on Single-Ended Inputs

Weak Pull-Up/-Down

IEEE 1149.1 (JTAG) Boundary Scan Test

Pin-Compatible Packages across the IGLOOe Family

Clock Conditioning Circuit (CCC) and PLL

Six CCC Blocks, Each with an Integrated PLL

Configurable Phase Shift, Multiply/Divide, Delay Capabilities,

and External Feedback

Wide Input Frequency Range (1.5 MHz up to 250 MHz)

Embedded Memory

1 kbit of FlashROM User Nonvolatile Memory

SRAMs and FIFOs with Variable-Aspect-Ratio 4,608-Bit RAM

Blocks (×1, ×2, ×4, ×9, and ×18 organizations available)

True Dual-Port SRAM (except ×18)

ARM Processor Support in IGLOOe FPGAs

M1 IGLOOe Devices—Cortex-M1 Soft Processor Available

with or without Debug

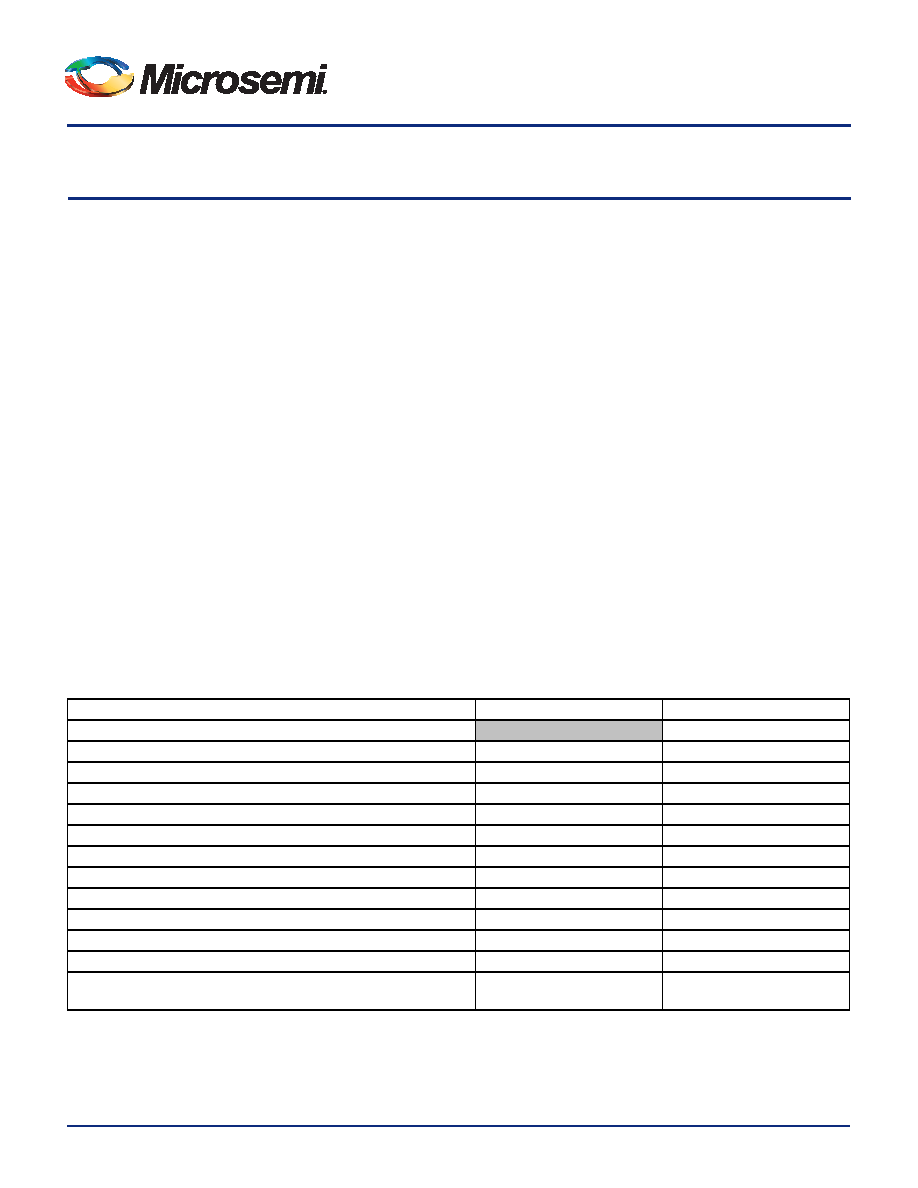

Table 1 IGLOOe Product Family

IGLOOe Devices

AGLE600

AGLE3000

ARM-Enabled IGLOOe Devices

M1AGLE3000

System Gates

600,000

3,000,000

VersaTiles (D-flip-flops)

13,824

75,264

Quiescent Current (typical) in Flash*Freeze Mode (W)

49

137

RAM kbits (1,024 bits)

108

504

4,608-Bit Blocks

24

112

FlashROM Kbits (1,024 bits)

1

Secure (AES) ISP

Yes

CCCs with Integrated PLLs

6

VersaNet Globals 1

18

I/O Banks

8

Maximum User I/Os

270

620

Package Pins

FBGA

FG256, FG484

FG484, FG896

Notes:

1. Refer to the Cortex-M1 Handbook for more information.

2. Six chip (main) and twelve quadrant global networks are available.

3. For devices supporting lower densities, refer to the IGLOO Low-Power Flash FPGAs with Flash*Freeze Technology datasheet.

Revision 13

相關PDF資料 |

PDF描述 |

|---|---|

| EP4CE55F29I8L | IC CYCLONE IV FPGA 55K 780FBGA |

| EP4CE55F29I7 | IC CYCLONE IV FPGA 55K 780FBGA |

| HCC60DRAI | CONN EDGECARD 120PS R/A .100 SLD |

| ACB80DHNT | CONN EDGECARD 160PS .050 DIP SLD |

| ABB80DHNT | CONN EDGECARD 160PS .050 DIP SLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AGLE600V5-FG896 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOOe Low-Power Flash FPGAs with Flash Freeze Technology |

| AGLE600V5-FG896ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOOe Low-Power Flash FPGAs with Flash Freeze Technology |

| AGLE600V5-FG896I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOOe Low-Power Flash FPGAs with Flash Freeze Technology |

| AGLE600V5-FG896PP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOOe Low-Power Flash FPGAs with Flash Freeze Technology |

| AGLE600V5-FGG256 | 功能描述:IC FPGA 1KB FLASH 600K 256-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:IGLOOe 標準包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購,3分鐘左右您將得到回復。