- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362278 > AM486DXSQFP 70NS, PLCC, IND TEMP(EEPROM) PDF資料下載

參數(shù)資料

| 型號(hào): | AM486DXSQFP |

| 英文描述: | 70NS, PLCC, IND TEMP(EEPROM) |

| 中文描述: | Am486DX采用SQFP - Am486DX采用SQFP包溫度比較 |

| 文件頁(yè)數(shù): | 30/52頁(yè) |

| 文件大小: | 1242K |

| 代理商: | AM486DXSQFP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

30

Am486DE2 Microprocessor

Auto Halt Restart

The Auto Halt Restart slot at register offset (word loca-

tion) 7F02h in SMRAM indicates to the SMI handler that

the SMI interrupted the CPU during a HALT state; bit 0

of slot 7F02h is set to 1 if the previous instruction was

a HALT (see Figure 10). If the SMI did not interrupt the

CPU in a HALT state, then the SMI microcode sets bit

0 of the Auto Halt Restart slot to 0. If the previous in-

struction was a HALT, the SMI handler can choose to

either set or reset bit 0. If this bit is set to 1, the RSM

microcode execution forces the processor to reenter the

HALT state. If this bit is set to 0 when the RSM instruction

is executed, the processor continues execution with the

instruction just after the interrupted HALT instruction. If

the HALT instruction is restarted, the CPU will generate

a memory access to fetch the HALT instruction (if it is

not in the internal cache), and execute a HALT bus cycle.

Table 8 shows the possible restart configurations. If the

interrupted instruction was not a HALT instruction (bit 0

is set to 0 in the Auto Halt Restart slot upon SMM entry),

setting bit 0 to 1 will cause unpredictable behavior when

the RSM instruction is executed.

I/O Trap Restart

The I/O instruction restart slot (register offset 7F00h in

SMRAM) gives the SMI handler the option of causing

the RSM instruction to automatically reexecute the in-

terrupted I/O instruction (see Figure 11).

When the RSM instruction is executed, if the I/O instruc-

tion restart slot contains the value 0FFh, then the CPU

automatically reexecutes the l/O instruction that the SMI

signal trapped. If the I/O instruction restart slot contains

the value 00h when the RSM instruction is executed,

then the CPU does not reexecute the I/O instruction.

The CPU automatically initializes the I/O instruction re-

start slot to 00h during SMM entry. The I/O instruction

restart slot should be written only when the processor

has generated an SMI on an I/O instruction boundary.

Processor operation is unpredictable when the I/O in-

struction restart slot is set when the processor is servic-

ing an SMI that originated on a non-I/O instruction

boundary.

If the system executes back-to-back SMI requests, the

second SMI handler must not set the I/O instruction re-

start slot. The second back-to-back SMI signal will not

have the I/O Trap Word set.

I/O Trap Word

The I/O Trap Word contains the address of the I/O ac-

cess that forced the external chipset to assert SMI,

whether it was a read or write access, and whether the

instruction that caused the access to the I/O address

was a valid I/O instruction. Table 9 shows the layout.

Bits 31–16 contain the I/O address that was being ac-

cessed at the time SMI became active. Bits 15–2 are

reserved.

If the instruction that caused the I/O trap to occur was a

valid I/O instruction (IN, OUT, INS, OUTS, REP INS, or

REP OUTS), the Valid I/O Instruction bit is set. If it was

not a valid I/O instruction, the bit is saved as a 0. For

REP instructions, the external chip set should return a

valid SMI within the first access.

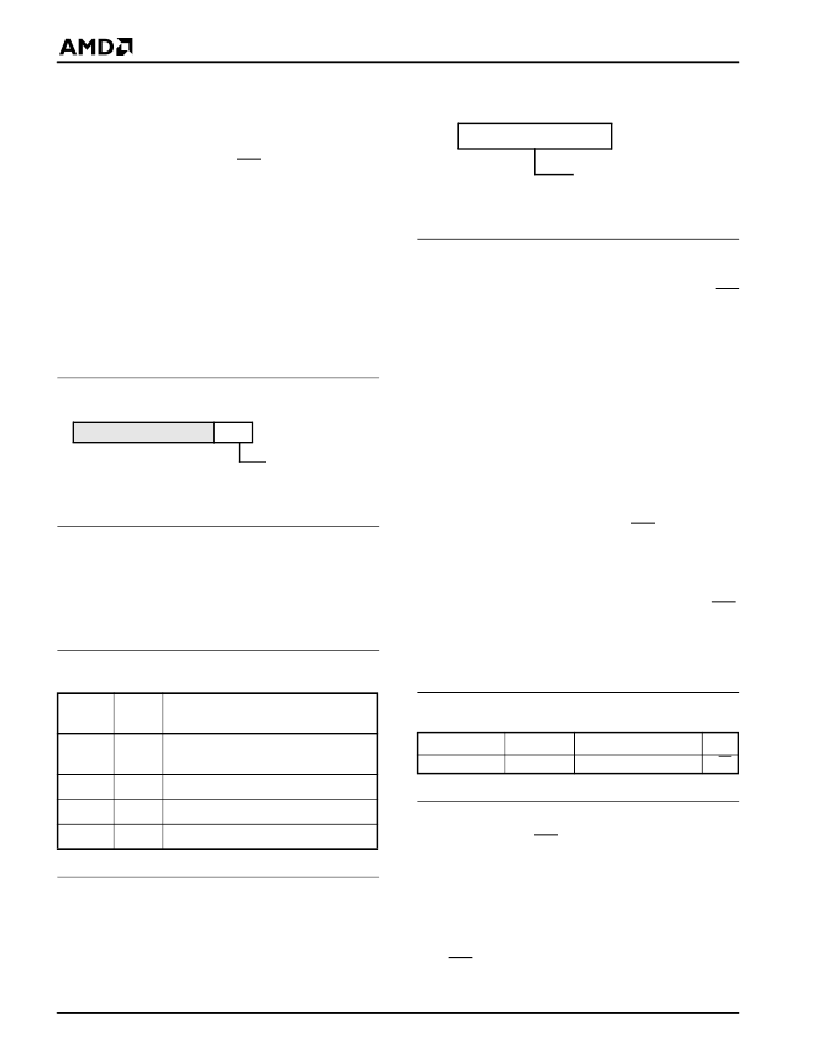

Figure 10. Auto Halt Restart Register Offset

Table 8. Auto Halt Restart Configuration

Value

at Entry

Value

at Exit

Processor Action on Exit

0

0

Return to next instruction in interrupted

program

0

1

Unpredictable

1

0

Returns to instruction after HALT

1

1

Returns to interrupted HALT instruction

Auto Halt Restart

Register Offset 7F02h

Reserved

15

1

0

Figure 11. I/O Instruction Restart Register Offset

Table 9. I/O Trap Word Configuration

31–16

15–2

1

0

I/O Address

Reserved

Valid I/O Instruction R/W

15

0

I/O instruction restart slot

Register offset 7F00h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM486 | Am486 Microprocessor Software User's Manual? 4.40MB (PDF) |

| AM49DL3208G | Am49DL3208G - Stacked Multi-Chip Package (MCP) Flash Memory and pSRAM |

| AM49DL320BG | Am49DL320BG - Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL32XBG | Am49DL32xBG - Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640BH | Am49DL640BH - Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM486-EVAL-KIT | 制造商:Advanced Micro Devices 功能描述:AM486CDP EVAL KIT |

| AM4874N | 制造商:ANALOGPOWER 制造商全稱:ANALOGPOWER 功能描述:N-Channel 30-V (D-S) MOSFET |

| AM4890N | 制造商:ANALOGPOWER 制造商全稱:ANALOGPOWER 功能描述:Dual N-Channel 150-V (D-S) MOSFET |

| AM4892N | 制造商:ANALOGPOWER 制造商全稱:ANALOGPOWER 功能描述:Dual N-Channel 150-V (D-S) MOSFET |

| AM48S-12-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。