- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366550 > AM79C901AVC (ADVANCED MICRO DEVICES INC) HomePHY Single-Chip 1/10 Mbps Home Networking PHY PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C901AVC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類(lèi): | 網(wǎng)絡(luò)接口 |

| 英文描述: | HomePHY Single-Chip 1/10 Mbps Home Networking PHY |

| 中文描述: | DATACOM, ETHERNET TRANSCEIVER, PQFP80 |

| 封裝: | PLASTIC, MO-136BAM, TQFP-80 |

| 文件頁(yè)數(shù): | 28/90頁(yè) |

| 文件大?。?/td> | 714K |

| 代理商: | AM79C901AVC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)

28

Am79C901A

P R E L I M I N A R Y

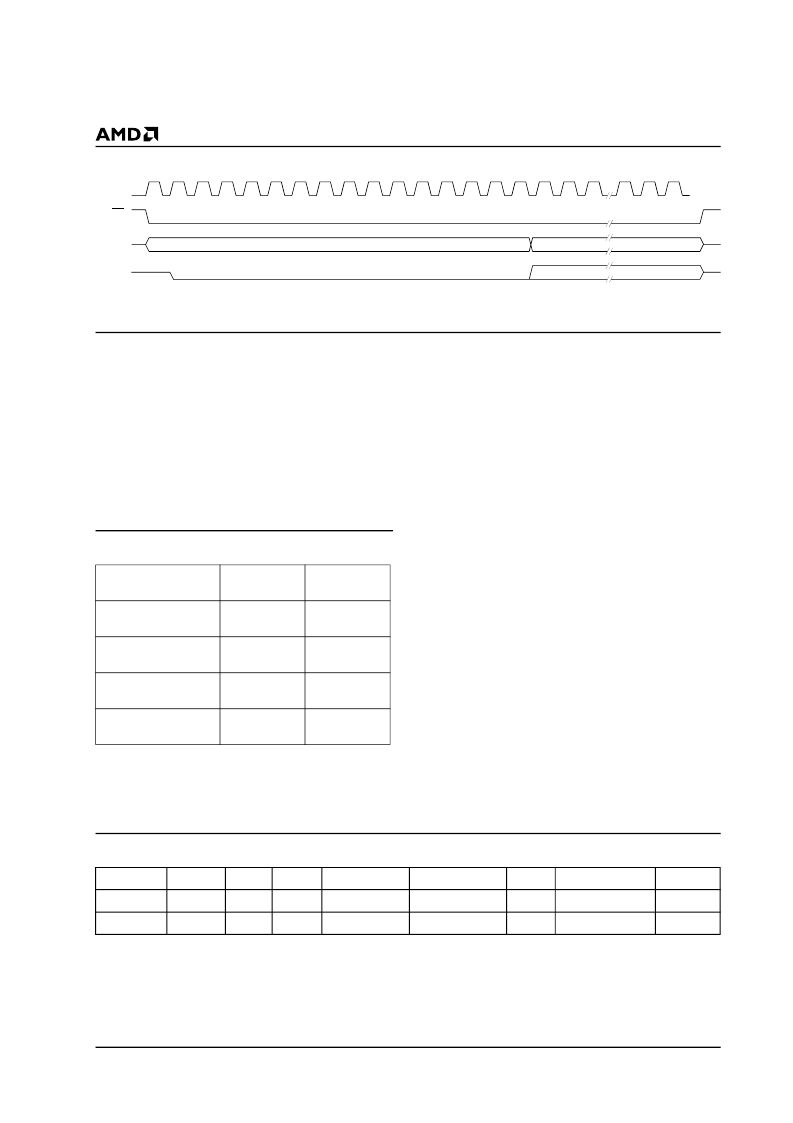

Figure 13.

Normal Operation

MII-Compatible Interface for HomePNA

PHY

The control and data signals that are utilized in the MII-

compatible interface of the 1 Mbps HomePNA PHY

function in an manner that is identical to that as defined

in the 802.3u specification. The signals RX_CLK and

TX_CLK function in a slightly different manner in that

they operate at a reduced data rate and that these

clock signals do not run at a constant rate due to the

RLL25

encoding scheme. See Table 4.

Table 4.

MII-Compatible Timing

Note:

During the AID interval, TX_CLK and RX_CLK

stop for up to 140

μ

s.

Figure 14 and Figure 15 represent the signal relation-

ships when the MII-compatible data interface is utilized.

The signals TX_CLK and RX_CLK will toggle at a rate

of approximately 428 kHz during idle time. When the

TX_EN signal is asserted to indicate the beginning of a

transmission, the clock rate will enter the preamble

phase. Once the SFD has been detected and the

HomePNA PHY has begun the transmission of the

HomePNA header, the clock enters the data phase.

When the TX_EN signal is deasserted to indicate the

ending of a transmission, TX_CLK is halted until the

RXDATA path detects the end of the packet. At this

time, the clock rate is increased to the IPG data rate for

96 bit times and then returns to the Idle state.

MII-Compliant Interface for 10BASE-T PHY

The MII interface is fully IEEE 802.3u-compliant when

the 10BASE-T PHY is selected. The management in-

terface specified in Clause 22 of the IEEE 802.3u stan-

dard provides for a simple two wire, serial interface to

connect a management entity and a managed PHY for

the purpose of controlling the PHY and gathering sta-

tus information. The two lines are Management Data

Input/Output (MDIO) and Management Data Clock

(MDC). A station management entity, which is attached

to multiple PHY entities, must have prior knowledge of

the appropriate PHY address for each PHY entity.

The management interface physically transports man-

agement information across the MII. The information

is encapsulated in a frame format as specified in

Clause 22 of the IEEE 802.3u standard and is shown

in Table 5.

Table 5.

MII Control Frame Format

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

30

31

32

Op Codes

Address

Data In

Data Out

Error Code = 0

SCLK

CS

SDI

SDO

22304B-15

Condition

CLK Period

CLK

Frequency

Idle (excluding IPG

time)

2333.34 ns

428.6 kHz

Preamble (first 64 bits

of TX MAC frame)

933.33 ns

1.07 MHz

Data (throughout the

data phase)

400 ns - 40

μ

s

250 kHz avg.

IPG (96 bit times

following CRS

↓

)

933.33 ns

1.07 MHz

PRE

ST

OP

PHYADD

REGADD

TA

DATA

IDLE

READ

1...1

01

10

AAAAA

RRRRR

Z0

D15

………

D0

Z

WRITE

1...1

01

01

AAAAA

RRRRR

10

D15

………

D0

Z

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C901AVCT | HomePHY Single-Chip 1/10 Mbps Home Networking PHY |

| AM79C901AVI | HomePHY Single-Chip 1/10 Mbps Home Networking PHY |

| AM79C901AVIT | HomePHY Single-Chip 1/10 Mbps Home Networking PHY |

| AM79C90 | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

| AM79C90JC | CMOS Local Area Network Controller for Ethernet (C-LANCE) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C901AVC/w | 制造商:Advanced Micro Devices 功能描述:79C901AVC/W |

| AM79C901AVC\\W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C901AVC\W | 制造商:Advanced Micro Devices 功能描述:PHY 1-CH 1Mbps/10Mbps 80-Pin TQFP |

| AM79C901AVCT | 制造商:AMD 制造商全稱(chēng):Advanced Micro Devices 功能描述:HomePHY Single-Chip 1/10 Mbps Home Networking PHY |

| AM79C901AVI | 制造商:AMD 制造商全稱(chēng):Advanced Micro Devices 功能描述:HomePHY Single-Chip 1/10 Mbps Home Networking PHY |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。