- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366551 > AM79C989JC (ADVANCED MICRO DEVICES INC) Quad Ethernet Switching Transceiver (QuEST⑩) PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C989JC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | Quad Ethernet Switching Transceiver (QuEST⑩) |

| 中文描述: | DATACOM, ETHERNET TRANSCEIVER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 19/37頁 |

| 文件大小: | 198K |

| 代理商: | AM79C989JC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

Am79C989

19

P R E L I M I N A R Y

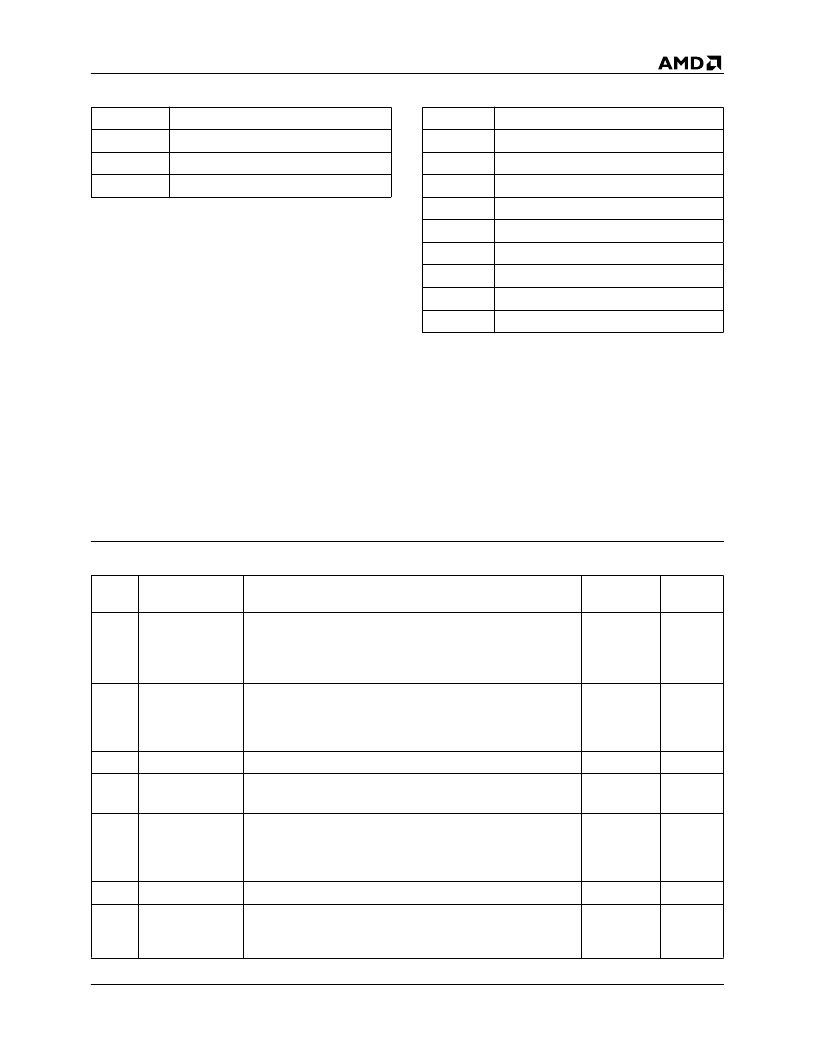

Table 5.

Shared Registers

Port Registers

Nine physical registers in the QuEST device are allo-

cated per port. Six of the port registers relate to Auto-

Negotiation. The remaining port registers are used for

control.

Registers 0, 1, 4-7, and 18-20 require an exact match

to specify the port being addressed. A particular regis-

ter is addressed by sending the serial management

frame with the target address of the designated port.

The lower two bits of the PHYAD (bits A1 and A0) spec-

ify which port is selected.

Table 6.

Port Registers

Non-Implemented Registers

Non-implemented registers should neither be written to

or read. Reserved register bits within defined registers

should be written with zeros.

Reserved register bits

may return undefined data and should be masked

by software.

Auto-Negotiation Control Register (Reg 0)

The Auto-Negotiation Control Register (Reg 0) con-

tains Read/Write (R/W), Read/Only (R/O), and Self-

Clearing (SC) bits. This register is duplicated for each

port.

Table 7.

Auto-Negotiation Control Register (Reg 0)

REGAD

Register Name

2-3

Device ID

16

Interrupt Enable and Status

17

Summary Status

REGAD

Register Name

0

Auto Negotiation Control

1

Auto Negotiation Status

4

Auto Negotiation Address

5

Auto Negotiation Link Partner

6

Auto Negotiation Expansion

7

Auto Negotiation Next Page

18

Control

19

Status

20

Error Mask

Bit(s)

Name

Description

Read/

Write

Default/

Reset

15

SRESET

1 = Resets the Auto Negotiation Control and Status registers to

their default state;

0 = Has no effect.

After reset is completed (approximately 10

μ

s), SRESET is cleared.

R/W, SC

0

14

Loopback

1 = Port will loop back the QTX_DATA to the QRX_DATA. Transmit

data will not be transmitted and receive data from the network will

be ignored.

0 = The port will receive and transmit normally.

R/W

0

13

Reserved

Written and read as zero.

R/O

0

12

ANEG_EN

1 = Auto-Negotiation enabled.

0 = Auto-Negotiation disabled.

R/W

1

11

PWR_DN

1 = 10BASE-T port Auto-Negotiation is reset. The Auto-Negotiation

process and Link Status State Machine will terminate. Link Test

Pulses will terminate.

0 = 10BASE-T port resumes normal operation.

R/W

0

10

Reserved

Written and read as zero.

R/O

0

9

Restart ANEG

1 = Auto-Negotiation restarts. The bit will be cleared when the Auto-

Negotiation process completes.

0 = Has no effect.

R/W, SC

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C989JCT | Quad Ethernet Switching Transceiver (QuEST⑩) |

| AM79C98 | Twisted-Pair Ethernet Transceiver (TPEX) |

| AM79C98JC | Twisted-Pair Ethernet Transceiver (TPEX) |

| AM79C98PC | Twisted-Pair Ethernet Transceiver (TPEX) |

| AM79D2251 | Dual Intelligent Subscriber Line Audio-Processing Circuit (ISLAC) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C989JC/T | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AM79C989JCT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Quad Ethernet Switching Transceiver (QuEST⑩) |

| AM79C98JC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Twisted-Pair Ethernet Transceiver (TPEX) |

| AM79C98JC/B | 制造商:Advanced Micro Devices 功能描述: 制造商:Advanced Micro Devices 功能描述:Part Number Only |

| AM79C98JCDV/B | 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。