- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362442 > AS4C256K16F0-35JC x16 Fast Page Mode DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | AS4C256K16F0-35JC |

| 英文描述: | x16 Fast Page Mode DRAM |

| 中文描述: | x16快速頁面模式的DRAM |

| 文件頁數(shù): | 2/25頁 |

| 文件大?。?/td> | 521K |

| 代理商: | AS4C256K16F0-35JC |

AS4C256K16FO

4/11/01;

V.0.9.1

Alliance Semiconductor

P. 2 of 25

Functional description

The AS4C256K16FO is a high-performance 4 megabit CMOS Dynamic Random Access Memory (DRAM) device organized as

262,144 words × 16 bits. The AS4C256K16FO is fabricated with advanced CMOS technology and designed with innovative

design techniques resulting in high speed, extremely low power and wide operating margins at component and system levels.

The AS4C256K16FO features a high-speed page mode operation in which high speed read, write and read-write are performed

on any of the 512

×

16 bits defined by the column address. The asynchronous column address uses an extremely short row

address capture time to ease the system-level timing constraints associated with multiplexed addressing. Output is tri-stated by a

column address strobe (CAS) which acts as an output enable independent of RAS. Very fast CAS to output access time eases

system design.

Refresh on the 512 address combinations of A0–A8 during an 8 ms period is accomplished by performing any of the following:

RAS-only refresh cycles

Hidden refresh cycles

CAS-before-RAS refresh cycles

Normal read or write cycles

Self-refresh cycles.

*

The AS4C256K16FO is available in standard 40-pin plastic SOJ and 44-pin TSOP II packages compatible with widely available

automated testing and insertion equipment. System level features include single power supply of 5V ± 10% tolerance and direct

interface with TTL logic families.

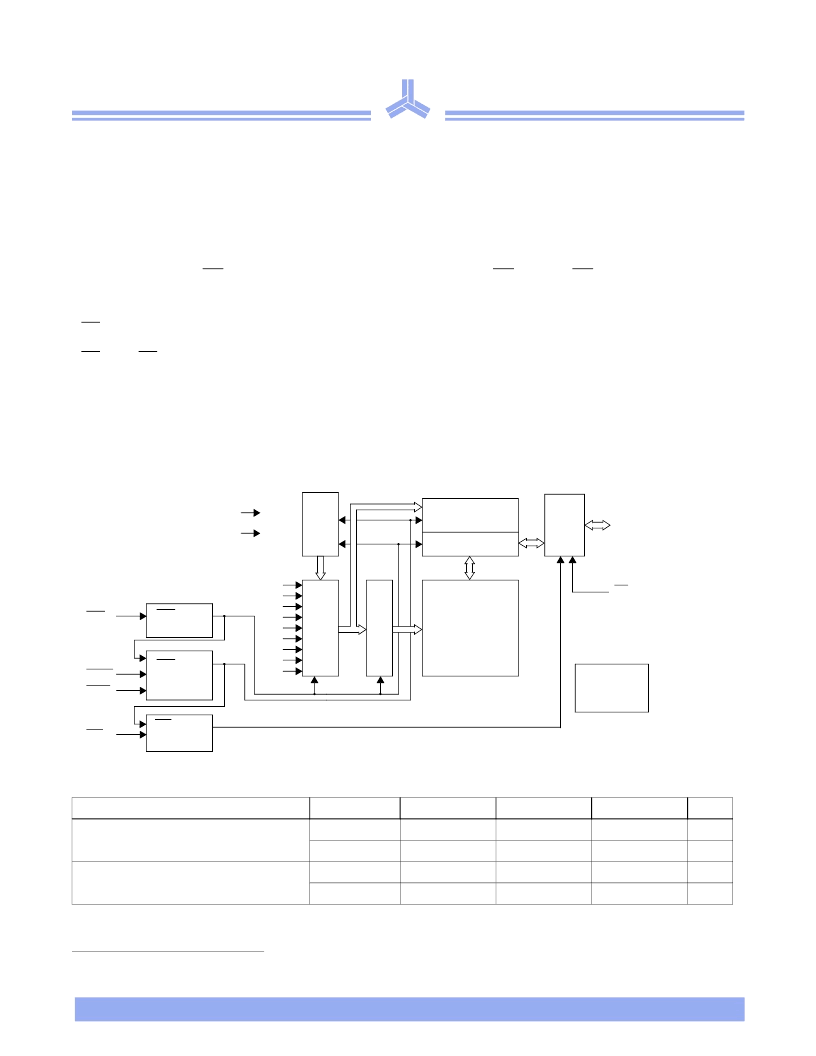

Logic block diagram

Recommended operating conditions

Parameter

* Self-refresh option is available for new generation device only. Contact Alliance for more information.

Symbol

Min

Typ

Max

Unit

Supply voltage

V

CC

GND

4.5

5.0

5.5

V

0.0

0.0

0.0

V

Input voltage

V

IH

V

IL

2.4

–

V

CC

+ 1

0.8

V

–1.0

–

V

512

×

512

×

16

array

(4,194,304)

Sense amp

A0

A1

A2

A3

A4

A5

A6

A7

A8

V

CC

GND

A

R

Column decoder

OE

RAS

UCAS

LCAS

WE

I/O0 to I/O15

Substrate

bias generator

Data

I/O

buffer

R

c

RAS clock

generator

CAS clock

generator

WE clock

generator

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS4C256K16F0-35JI | x16 Fast Page Mode DRAM |

| AS4C256K16F0-35TC | x16 Fast Page Mode DRAM |

| AS4C4M4 | 16384Kbits 4M x 4 Replacement with DSCC 5962-n/a | DRAM |

| AS4C4M4E0-70JC | x4 EDO Page Mode DRAM |

| AS4C4M4E1-50JC | x4 EDO Page Mode DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS4C256K16F0-35JI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x16 Fast Page Mode DRAM |

| AS4C256K16F0-35TC | 制造商:ALSC 制造商全稱:Alliance Semiconductor Corporation 功能描述:5V 256K X 16 CMOS DRAM (Fast Page Mode) |

| AS4C256K16F0-35TI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x16 Fast Page Mode DRAM |

| AS4C256K16F0-50JC | 制造商:ALSC 制造商全稱:Alliance Semiconductor Corporation 功能描述:5V 256K X 16 CMOS DRAM (Fast Page Mode) |

| AS4C256K16F0-50JI | 制造商:ALSC 制造商全稱:Alliance Semiconductor Corporation 功能描述:5V 256K X 16 CMOS DRAM (Fast Page Mode) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。