- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295111 > AT40K40LV-3FQC (ATMEL CORP) FPGA, 2304 CLBS, 40000 GATES, PQFP304 PDF資料下載

參數(shù)資料

| 型號: | AT40K40LV-3FQC |

| 廠商: | ATMEL CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 2304 CLBS, 40000 GATES, PQFP304 |

| 封裝: | PLASTIC, QFP-304 |

| 文件頁數(shù): | 12/67頁 |

| 文件大小: | 1589K |

| 代理商: | AT40K40LV-3FQC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

2

AT40K/AT40KLV Series FPGA

0896C–FPGA–04/02

Note:

1. Packages with FCK will have 8 less registers.

Description

The AT40K/AT40KLV is a family of fully PCI-compliant, SRAM-based FPGAs with dis-

tributed 10 ns programmable synchronous/asynchronous, dual-port/single-port SRAM,

8 global clocks, Cache Logic ability (partially or fully reconfigurable without loss of data),

automatic component generators, and range in size from 5,000 to 50,000 usable gates.

I/O counts range from 128 to 384 in industry standard packages ranging from 84-pin

PLCC to 352-ball Square BGA, and support 5V designs for AT40K and 3.3V designs for

AT40KLV.

The AT40K/AT40KLV is designed to quickly implement high-performance, large gate

count designs through the use of synthesis and schematic-based tools used on a PC or

Sun platform. Atmel’s design tools provide seamless integration with industry standard

tools such as Synplicity, ModelSim, Exemplar and Viewlogic.

The AT40K/AT40KLV can be used as a coprocessor for high-speed (DSP/processor-

based) designs by implementing a variety of computation intensive, arithmetic functions.

These include adaptive finite impulse response (FIR) filters, fast Fourier transforms

(FFT), convolvers, interpolators and discrete-cosine transforms (DCT) that are required

for video compression and decompression, encryption, convolution and other multime-

dia applications.

Fast, Flexible and

Efficient SRAM

The AT40K/AT40KLV FPGA offers a patented distributed 10 ns SRAM capability where

the RAM can be used without losing logic resources. Multiple independent, synchronous

or asynchronous, dual-port or single-port RAM functions (FIFO, scratch pad, etc.) can

be created using Atmel’s macro generator tool.

Fast, Efficient Array and

Vector Multipliers

The AT40K/AT40KLV’s patented 8-sided core cell with direct horizontal, vertical and

diagonal cell-to-cell connections implements ultra fast array multipliers without using

any busing resources. The AT40K/AT40KLV’s Cache Logic capability enables a large

number of design coefficients and variables to be implemented in a very small amount

of silicon, enabling vast improvement in system speed at much lower cost than conven-

tional FPGAs.

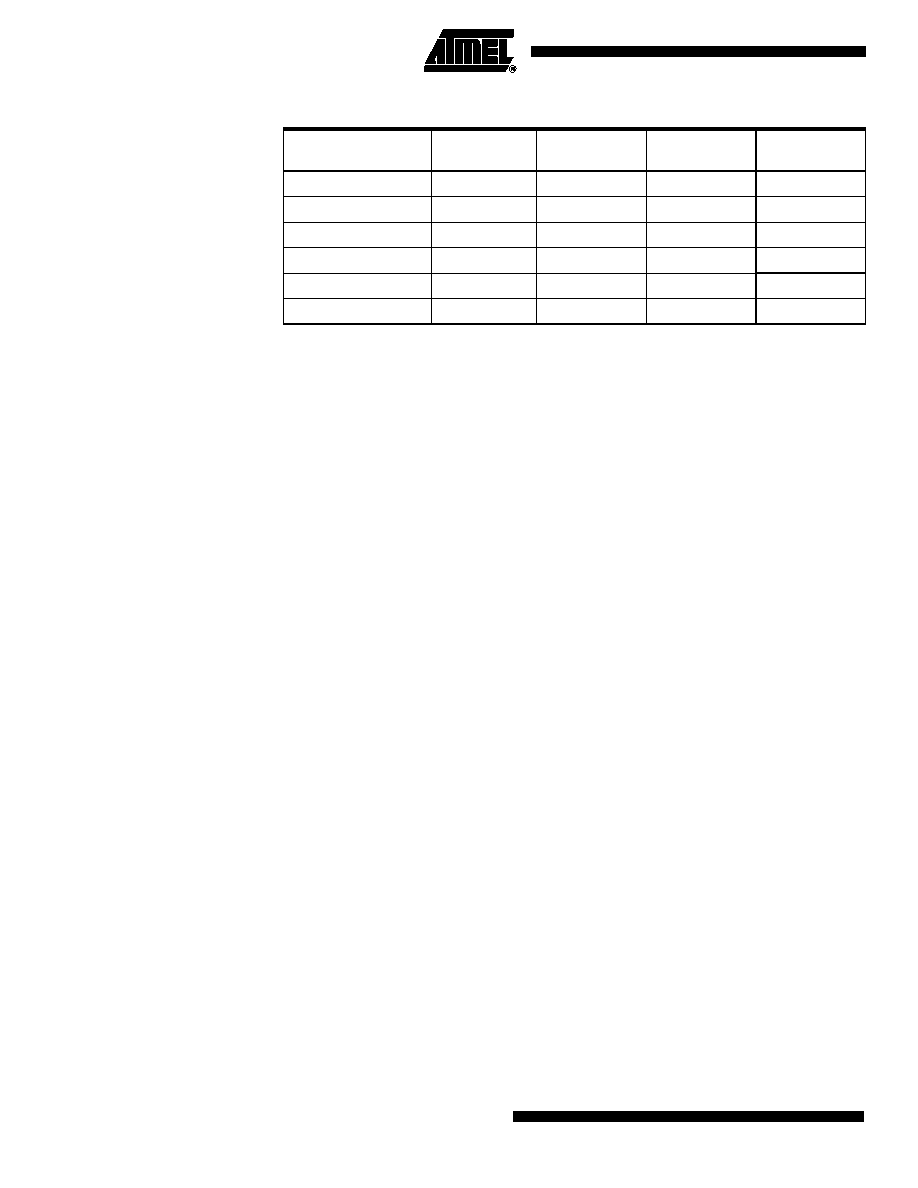

Table 1. AT40K/AT40KLV Family

Device

AT40K05

AT40K05LV

AT40K10

AT40K10LV

AT40K20

AT40K20LV

AT40K40

AT40K40LV

Usable Gates

5K - 10K

10K - 20K

20K - 30K

40K - 50K

Rows x Columns

16 x 16

24 x 24

32 x 32

48 x 48

Cells

256

576

1,024

2,304

Registers

576

1,024

2,304

RAM Bits

2,048

4,608

8,192

18,432

I/O (Maximum)

128

192

256

384

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT40KEL040KW1SB | FPGA, 2304 CLBS, 50000 GATES, PQFP160 |

| AT40KEL040KZ1SB | FPGA, 2304 CLBS, 50000 GATES, PQFP256 |

| AT89C2051-12SCT/R | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PDSO20 |

| AT89C51-24JCT/R | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PQCC44 |

| AT89C55-12JA | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT40K40LV-3FQI | 功能描述:IC FPGA 3.3V 2304 CELL 304PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:AT40K/KLV 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| AT40KAL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:AT40KAL Preliminary [Updated 6/03. 38 Pages] |

| AT40KAL040KW1M | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Military Reprogrammable FPGAs with FreeRAM |

| AT40KAL040KW1M-E | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Military Reprogrammable FPGAs with FreeRAM |

| AT40KAL040KW1MMQ | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Military Reprogrammable FPGAs with FreeRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。