- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223464 > BU-66318G0-110 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PQFP208 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-66318G0-110 |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PQFP208 |

| 封裝: | 28 X 28 MM, 1.40 MM HEIGHT, LQFP-208 |

| 文件頁(yè)數(shù): | 19/32頁(yè) |

| 文件大小: | 278K |

| 代理商: | BU-66318G0-110 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

26

Data Device Corporation

www.ddc-web.com

BU-66318

B-09/05-0

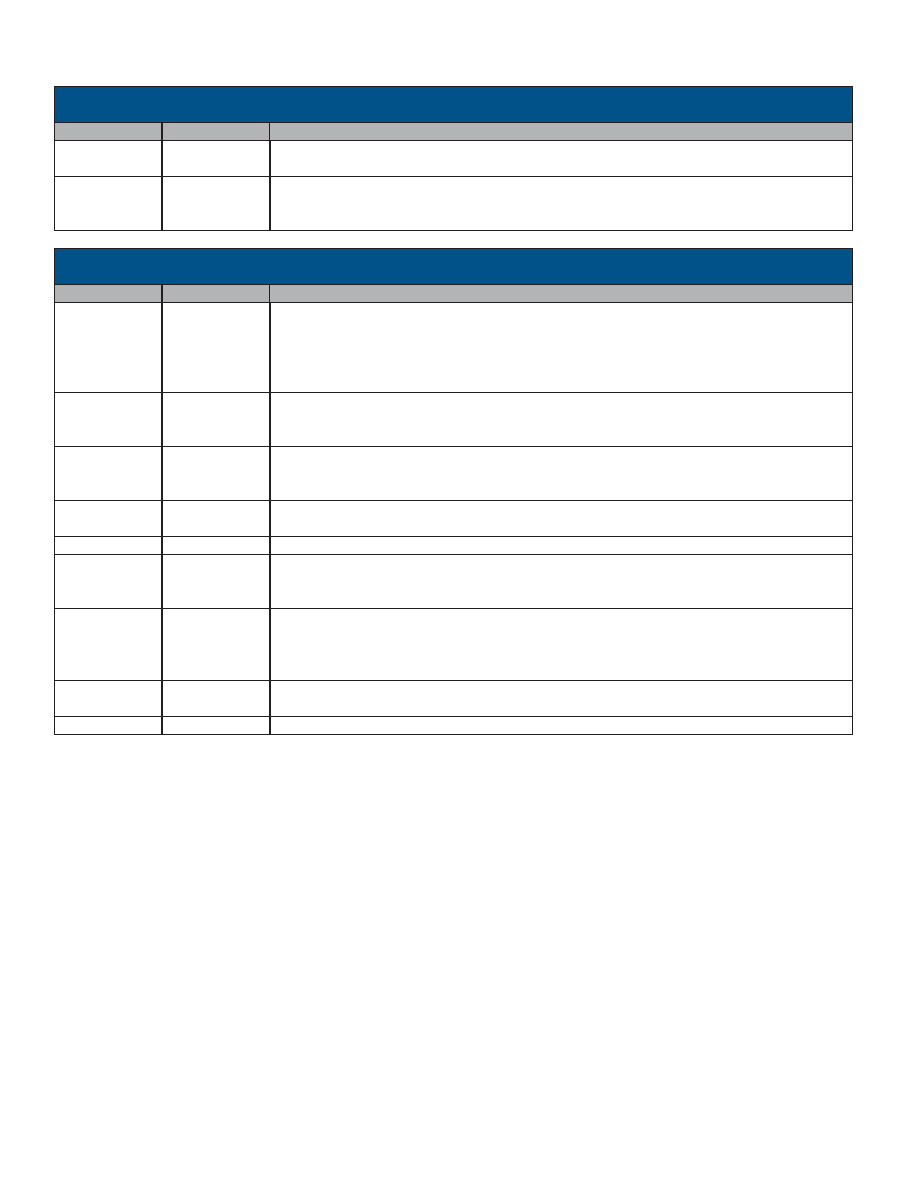

TABLE 28. PCI BUS SYSTEM SIGNALS

SIGNAL NAME

PIN

DESCRIPTION

PCI_CLK_IN (I)

172

RST# (I)

88

Clock input. The rising edge of this signal is the reference upon which all other clock signals are based, with

the exception of RST# and INTA#. The maximum frequency accepted is 33 MHz and the minimum is 0 Hz.

Reset. This signal is used to bring all other signals within this device, and on the local bus, to a known,

consistent state. All PCI bus interface output signals are not driven (tri-stated), and open drain signals are

floated.

TABLE 29. PCI BUS CONTROL SIGNALS

SIGNAL NAME

PIN

DESCRIPTION

FRAME#(I)

25

IRDY#(I)

27

TRDY#(O)

34

STOP#(O)

41

IDSEL(I)

13

DEVSEL#(O)

33

PERR#(O)

40

SERR#(O)

42

INTA#(O)

15

Frame. This signal is driven by the current bus master and identifies both the beginning and duration of a

bus operation. When FRAME# is first asserted, it indicates that a bus transaction is beginning and that

valid addresses and a corresponding bus command are present on the AD[31:0] and C/BE[3:0] lines.

FRAME# remains asserted during the data transfer portion of a bus operation and is deasserted to signify

the final data phase.

Initiator Ready. This signal is sourced by the bus master and indicates that the bus master is able to com-

plete the current data phase of a bus transaction. For write operations, it indicates that valid data is on the

AD[31:0] pins. Wait states occur until both TRDY# and IRDY# are asserted together.

Target Ready. This signal is sourced by the selected target and indicates that the target is able to complete

the current data phase of a bus transaction. For read operations, it indicates that the target is providing

valid data is on the AD[31:0] pins. Wait states occur until both TRDY# and IRDY# are asserted together.

Stop. The Stop signal is sourced by the selected target and conveys a request to the bus master to stop

the current transaction.

Initialization Device Select. This pin is used as a chip select during configuration read or write operations.

Device Select. This signal is sourced by an active target upon decoding that its address and bus com-

mands are valid. For bus masters, it indicates whether any device has decoded the current bus cycle.

(The BU-66318 operates as a target agent only)

Parity Error. This pin is used for reporting parity errors during the data portion of the bus transaction for all

cycle except a Special Cycle. It is sourced by the agent receiving data and driven active two clocks follow-

ing the detection of an error. This signal is driven inactive (high) two clocks prior to returning to the tri-state

condition.

System Error. This pin is used for reporting address parity errors, data parity errors on Special Cycle com-

mands, or any other condition having a catastrophic system impact.

Interrupt A. This pin is a level sensitive, active low interrupt to the host.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU2294AF | 67.735842 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| BU3076HFV-TR | 67.5 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| BU6836 | PCMCIA BUS CONTROLLER, PBGA256 |

| BU7346GUL | 38 MHz, OTHER CLOCK GENERATOR, PBGA6 |

| BUF01900AIDRCR | SPECIALTY ANALOG CIRCUIT, PDSO10 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU6650NUX | 制造商:ROHM 制造商全稱:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX_11 | 制造商:ROHM 制造商全稱:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX-TR | 功能描述:低壓差穩(wěn)壓器 - LDO LDO REG 0.2A 8PIN 2.8V 2.8V 1.8V RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| BU6651NUX | 制造商:ROHM 制造商全稱:Rohm 功能描述:High-speed Load Response Full CMOS LDP Regulators |

| BU6651NUX-TR | 功能描述:低壓差穩(wěn)壓器 - LDO LDO REG 0.2A 8PIN 2.8V 1.8V 1.5V RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。