- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384185 > CDC930DL CPU SYSTEM CLOCK GENERATOR|SSOP|56PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | CDC930DL |

| 英文描述: | CPU SYSTEM CLOCK GENERATOR|SSOP|56PIN|PLASTIC |

| 中文描述: | CPU系統(tǒng)時鐘發(fā)生器| SSOP封裝| 56PIN |塑料 |

| 文件頁數(shù): | 9/17頁 |

| 文件大小: | 240K |

| 代理商: | CDC930DL |

CDC930

133-MHz DIFFERENTIAL CLOCK SYNTHESIZER/DRIVER FOR PC MOTHERBOARDS

WITH 3-STATE OUTPUTS

SCAS641 – JULY 2000

9

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

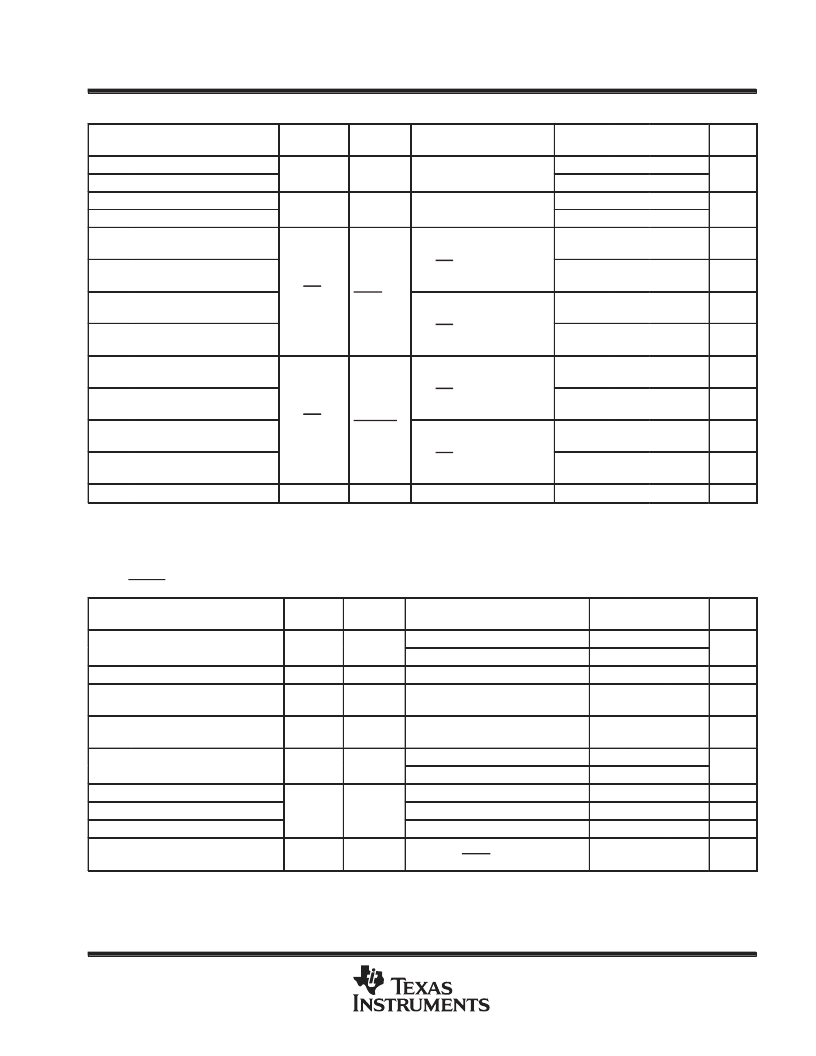

switching characteristics, V

DD

= MIN to MAX, T

A

= 0

°

C to 85

°

C

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

TEST CONDITIONS

MIN

TYP

MAX

UNIT

vover

vunder

vover

vunder

Overshoot

Undershoot

Overshoot

Undershoot

HCLK/HCLK 0.7 V ampli-

tude

VOH+200

VOL–200

mV

Other clocks, CL

case

GND–0.7

V

VDD+0.7

tPZL

Output enable time to low

level

f(HCL) = 100 or 133 MHz,

SELA, SELB = H,

SEL100/133 L

→

H,

Rref = 475

100

ns

tPZH

Output enable time to high

level

SEL100/133

HCLK/

HCLK

100

ns

tPHZ

Output disable time from

high level

f(HCL) = 100 or 133 MHz,

SELA, SELB = H,

SEL100/133 H

→

L,

Rref = 475

10

ns

tPLZ

Output disable time from low

level

10

ns

tPZL

Output enable time to low

level

f(HCL) = 100 or 133 MHz,

SELA, SELB = H,

SEL100/133 L

→

H,

Rref = 475

10

ns

tPZH

Output enable time to high

level

SEL100/133

REF, 3V48

3VMREF,

3VMREF,

3V66, PCI

10

ns

tPHZ

Output disable time from

high level

f(HCL) = 100 or 133 MHz,

SELA, SELB = H,

SEL100/133 H

→

L,

Rref = 475

After power up

10

ns

tPLZ

Output disable time from low

level

Stabilization time

Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal. In order for

phase lock to be obtained, a fixed-frequency, fixed-phase reference signal must be present a XIN. Until phase lock is obtained, the specifications

for propagation delay and skew parameters given in the switching characteristics tables are not applicable. Stabilization time is defined as the

time from when VDD achieves its nominal operating level until the output frequency is stable and operating within specification.

These parameters are ensured by design and lab characterization, not 100% production tested.

10

ns

tstab

3

ms

HCLK/HCLK (Type X1) C

L

= 2 pF, R

L

> 500 k

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

TEST CONDITIONS

MIN

TYP

MAX

UNIT

tc

HCLK clock period

f(HCLK) = 100 MHz

f(HCLK) = 133 MHz

f(HCLK = 100 or 133 MHz

f(HCLK) = 100 or 133 MHz crossing

point

10

10.2

ns

7.5

7.65

tjit(cc)

Cycle to cycle jitter

200

ps

tdc

Duty cycle

45%

55%

tsk(o)

HCLK bus skew

HCLKx

HCLKx

f(HCLK) = 100 or 133 MHz crossing

point

150

ps

tw

Pulse duration width

f(HCLK = 100 MHz

f(HCLK = 133 MHz

VO = 0.14 V to 0.56 V

VO = 0.14 V to 0.56 V

2

×

(tr – tf)/(tr + tf)

f(HCLK) = 100 or 133 MHz

HCLK and HCLK

4.41

ns

3.29

tr

tf

tr, tf

Rise time

0 7 V

0.7 V

amplitude

am litude

175

700

ps

Fall time

Rise and fall time matching

175

700

ps

20%

vcross

Cross point voltages

0.7 V

amplitude

40%

VOH

55%

VOH

V

The average over any 1–

μ

s period of time is greater than the minimum specified period.

These parameters are ensured by design and lab characterization, not 100% production tested.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CDD1933 | TRANSISTOR | BJT | DARLINGTON | NPN | 80V V(BR)CEO | 4A I(C) | SOT-32 |

| CDD2061D | TRANSISTOR | BJT | NPN | 60V V(BR)CEO | 3A I(C) | TO-220AB |

| CDD2061E | TRANSISTOR | BJT | NPN | 60V V(BR)CEO | 3A I(C) | TO-220AB |

| CDD2061F | TRANSISTOR | BJT | NPN | 60V V(BR)CEO | 3A I(C) | TO-220AB |

| CDD2061G | TRANSISTOR | BJT | NPN | 60V V(BR)CEO | 3A I(C) | TO-220AB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CDC930DLG4 | 功能描述:鎖相環(huán) - PLL 133-MHz Clock Synth/ Drvr RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CDC930DLR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CDC950 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:133-MHz DIFFERENTIAL CLOCK SYNTHESIZER/DRIVER FOR PC MOTHERBOARDS/SERVERS |

| CDC950DGG | 功能描述:時鐘合成器/抖動清除器 133MHz Clk Synth RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| CDC950DGGG4 | 功能描述:時鐘合成器/抖動清除器 133MHz Clk Synth RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。