- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366891 > CR16MCS9VJE7Y Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CR16MCS9VJE7Y |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 34/157頁(yè) |

| 文件大小: | 1256K |

| 代理商: | CR16MCS9VJE7Y |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)

www.national.com

34

— Interrupt Status Register 0 (ISTAT0)

— Interrupt Status Register 1 (ISTAT1)

— Interrupt Debug Register (IDBG)

The following CPU core registers are also used in processing

interrupts:

— Interrupt Stack Pointer (ISP)

— Interrupt Base Register (INTBASE)

10.4.1

Non-Maskable Interrupt Status Register

(NMISTAT)

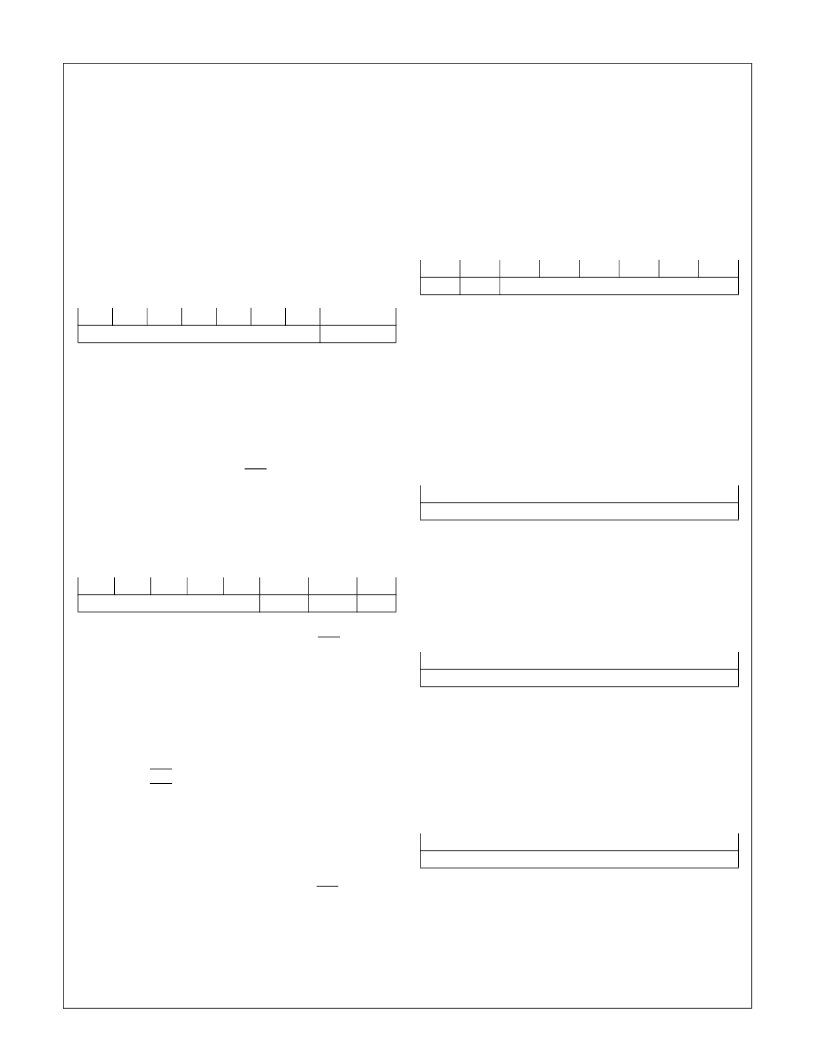

The NMISTAT register is a byte-wide, read-only register that

holds the current pending status of the Non-Maskable Inter-

rupt (NMI). This register is cleared upon reset. It is also

cleared each time it is read. The register format is shown be-

low.

7

6

5

4

3

Reserved

EXT

External Non-Maskable Interrupt Request.

When set to 1 by the hardware, it indicates an

external Non-Maskable Interrupt request has

occurred. See the description of the EXNMI

register below for more information.

10.4.2

The EXNMI register is a byte-wide, read/write register that

shows the current state of the NMI pin and also allows the

NMI trap to be enabled by setting either the EN bit or the EN-

LCK bit. Both of these bits are cleared upon reset. When the

software writes to this register, it must write 0 to all reserved

bit positions for the device to function properly. EN, ENLCK,

and TST are cleared upon reset. The register format is

shown below.

7

6

5

4

Reserved

External NMI Control/Status Register (EXNMI)

EN

Enable NMI Trap. When set to 1, NMI traps are

enabled and falling edge on the NMI pin gener-

ates a NMI trap. Each occurrence of an NMI

trap automatically clears the EN bit. The trap

service routine should set the EN bit to 1 before

returning control to the interrupted program.

When EN is cleared to 0, NMI traps are dis-

abled unless they are enabled with the ENLCK

bit. When the ENLCK bit is set to 1, the EN bit

is ignored.

NMI Pin. This bit shows the current state of the

NMI input pin (without logical inversion). A 1 in-

dicates a high level and a 0 indicates a low lev-

el on the pin. This is a read-only bit. In a write

operation, the value written to this bit position is

ignored.

Enable and Lock NMI Trap. When set to 1, NMI

traps are enabled and locked in the enabled

state. Each falling edge on the NMI pin gener-

ates a NMI trap, even if a previous NMI trap has

occurred and is still being processed. When

ENLCK is cleared to 0, NMI traps are disabled

unless they are enabled with the EN bit.

PIN

ENLCK

10.4.3

The IVCT register is a byte-wide, read-only register that con-

tains the encoded value of the enabled and pending

maskable interrupt with the highest priority. The on-chip hard-

ware automatically updates this field whenever there is a

change in the highest-priority enabled and pending maskable

interrupt. The CPU reads this register during an interrupt ac-

knowledge core bus cycle to determine where to begin exe-

cuting the interrupt service routine. The register contents are

guaranteed to be valid at that time. The register is not guar-

anteed to contain valid data during a hardware update oper-

ation. The register format is shown below.

7

6

5

4

0

0

Interrupt Vector Register (IVCT)

INTVECT

Interrupt Vector. This 6-bit field contains the en-

coded value of the enabled and pending

maskable interrupt with the highest priority. For

example, if interrupts IRQ1 and IRQ6 are both

enabled and pending, the higher-priority inter-

rupt is IRQ6. As a result the 6 bit interrupt vec-

tor is 010110.

10.4.4

The IENAM0 register is a word-wide, read/write register that

enables or disables the individual interrupts IRQ0 through

IRQ15. The register format is shown below.

15

IENA(15:0)

Interrupt Enable and Mask Register 0 (IENAM0)

A bit set to 1 enables the corresponding interrupt. A bit

cleared to 0 disables the corresponding interrupt. Upon re-

set, this register is initialized to FFFF hex.

10.4.5

The IENAM0 register is a word-wide, read/write register that

enables or disables the individual interrupts IRQ16 through

IRQ31. The register format is shown below.

15

IENA(31:16)

Interrupt Enable and Mask Register 1 (IENAM1)

A bit set to 1 enables the corresponding interrupt. A bit

cleared to 0 disables the corresponding interrupt. Upon re-

set, this register is initialized to FFFF hex.

10.4.6

The ISTAT0 register is a word-wide, read-only register that

indicates which maskable interrupt inputs to the ICU31L

(IRQ0 through IRQ15) are currently active. The register for-

mat is shown below.

15

IST(15:0)

Interrupt Status Register 0 (ISTAT0)

IST(15:0)

Interrupt Status bits. Each bit indicates the cur-

rent status of an interrupt input to the ICU31L,

corresponding to interrupts IRQ0 through

IRQ15. A bit set to 1 indicates an active inter-

rupt input, even when the interrupt is masked

out by the IENAM0 register. A bit cleared to 0

indicates an inactive interrupt input.

2

1

0

EXT

3

2

1

0

ENLCK

PIN

EN

3

INTVECT

2

1

0

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16MCS9VJE8 | Microcontroller |

| CR16MCS9VJE8Y | Microcontroller |

| CR16MCT5VJE7Y | Microcontroller |

| CR16HCS5VJE8 | Microcontroller |

| CR16HCS9VJE7Y | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16MCS9VJE8 | 功能描述:16位微控制器 - MCU RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| CR16MCS9VJE8/NOPB | 功能描述:16位微控制器 - MCU RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| CR16MCS9VJE80 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Family of 16-bit CAN-enabled CompactRISC Microcontrollers |

| CR16MCS9VJE81 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Family of 16-bit CAN-enabled CompactRISC Microcontrollers |

| CR16MCS9VJE82 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Family of 16-bit CAN-enabled CompactRISC Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。