- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄26509 > CS42L52-DNZR (CIRRUS LOGIC INC) PDF資料下載

參數(shù)資料

| 型號: | CS42L52-DNZR |

| 廠商: | CIRRUS LOGIC INC |

| 元件分類: | 消費家電 |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, LEAD FREE, MO-220, QFN-40 |

| 文件頁數(shù): | 44/59頁 |

| 文件大小: | 1800K |

| 代理商: | CS42L52-DNZR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

DS680F1

49

CS42L52

5/13/08

6.8.2

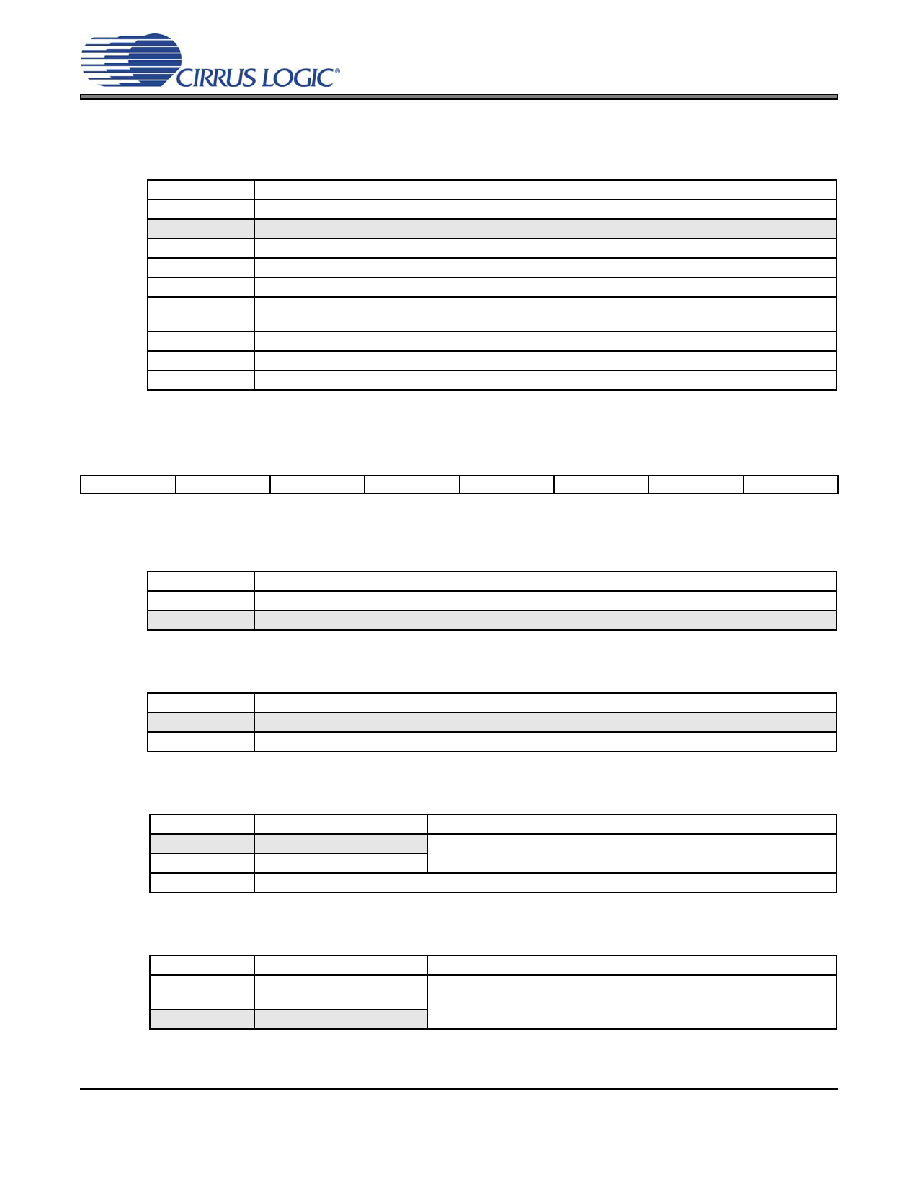

PGA Input Mapping

Selects one or sums/mixes the analog input signal into the PGA. Each bit of the PGAx_SEL[5:1] word

corresponds to individual channels (i.e. PGAx_SEL1 selects AIN1x, PGAx_SEL2 selects AIN2x, etc.).

6.9

Analog & HPF Control (Address 0Ah)

6.9.1

ADCx High-Pass Filter

Configures the internal high-pass filter after ADCx.

6.9.2

ADCx High-Pass Filter Freeze

Configures the high pass filter’s digital DC subtraction and/or calibration after ADCx.

6.9.3

Ch. x Analog Soft Ramp

Configures an incremental volume ramp from the current level to the new level at the specified rate.

6.9.4

Ch. x Analog Zero Cross

Configures when the signal level changes occur for the analog volume controls.

Note:

If the signal does not encounter a zero crossing, the requested volume change will occur after a

timeout period of 1024 sample periods (approximately 10.7 ms at 48 kHz sample rate).

PGAxSEL[5:1]

Selected Input to PGAx

(Examples)

00000

No inputs selected

00001

AIN1x

00010

AIN2x

00100

AIN3x

01000

AIN4x

10000

MICx;

for single-ended MIC inputs, use MICxSEL (“MIC x Select” on page 55) to select MIC 1 or MIC 2; for

differential MIC inputs, enable MICxCFG (“MICx Configuration” on page 55)

10001

MICx + AIN1x

10011

MICx + AIN1x + AIN2x

Application:

Note: Table does not show all possible combinations.

7

6

5

432

10

HPFB

HPFRZB

HPFA

HPFRZA

ANLGSFTB

ANLGZCB

ANLGSFTA

ANLGZCA

HPFx

High Pass Filter Status

0

Disabled

1

Enabled

HPFRZx

High Pass Filter Digital Subtraction

0

Continuous DC Subtraction

1

Frozen DC Subtraction

ANLGSFTx

Volume Changes

Affected Analog Volume Controls

0

Do not occur with a soft ramp

MICxGAIN[4:0] (“MICx Gain” on page 55), PGAxVOL[5:0] (“PGAx Volume”

on page 56), and PASSxVOL[7:0] (“Passthrough x Volume” on page 57)

1

Occur with a soft ramp

Ramp Rate:

1/2 dB every 16 LRCK cycles

ANLGZCx

Volume Changes

Affected Analog Volume Controls

0

Do not occur on a zero cross-

ing

MICxGAIN[4:0] (“MICx Gain” on page 55), PGAxVOL[5:0] (“PGAx Volume”

on page 56), and PASSxVOL[7:0] (“Passthrough x Volume” on page 57)

1

Occur on a zero crossing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CS42L73-CWZR | |

| CS4354-CSZ | |

| CS47028C-DQZ | |

| CS47048C-CQZ | |

| CS47024C-CQZ | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS42L55 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:Ultra Low Power, Stereo CODEC w/Class H Headphone Amp |

| CS42L55-CNZ | 功能描述:接口—CODEC IC Ultra Low Power Stereo Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| CS42L55-CNZR | 功能描述:接口—CODEC IC Ultra Low PWR Stereo Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| CS42L55-DNZ | 功能描述:接口—CODEC Portble Stereo CODEC Class H HP Amp RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| CS42L55DNZR | 制造商:Cirrus Logic 功能描述:PORTABLE STEREO CODEC AND UNIQUE CLASS H HP AMP AUTO GRADE & - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。