- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378470 > CXD2510Q (Sony Corporation) CD Digital Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | CXD2510Q |

| 廠商: | Sony Corporation |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | CD Digital Signal Processor |

| 中文描述: | CD數(shù)字信號(hào)處理器 |

| 文件頁數(shù): | 37/48頁 |

| 文件大小: | 743K |

| 代理商: | CXD2510Q |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

– 37 –

CXD2510Q

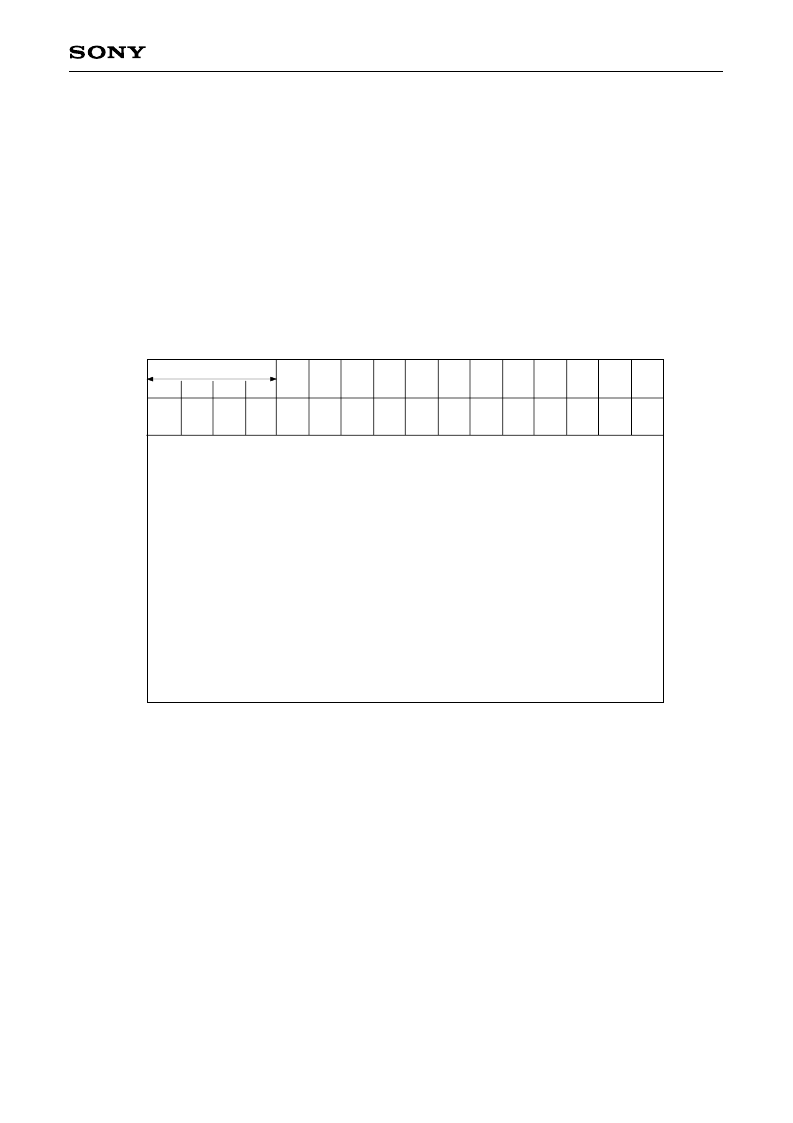

§3-5. Digital Out

There are three digital out formats: the type 1 format for broadcasting stations, the type 2 form 1 format for

home use, and the type 2 form 2 format for the manufacture of software.

The CXD2510Q supports type 2 form 1.

In addition, regarding the clock accuracy of the channel status, level

III

is set automatically when the crystal

clock is used and level

II

is variable pitch. In addition, Sub Q data which are matched twice in succession

after a CRC check are input to the first four bits (bit 0 to 3).

DOUT is output when the crystal is 34MHz, the variable pitch is reset, and DSPB = 1. Therefore, set MD2 to

0 and turn DOUT off.

bit 0 to 3 -Sub Q control bits that matched twice with CRCOK

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0/1

0

0

0

ID0

ID1 COPY Emph

0

0

0

0

1

0

0

0

0

0

0

0

From sub Q

0

16

32

48

176

– Sub Q control bits that matched twice with CRCOK

Digital Out C bit

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

– Varipitch: 1

X'Tal: 0

bit 0 to 3

bit29

Table 3-6.

§3-6. Servo Auto Sequence

This function performs a series of controls, including auto focus and track jumps. When the auto sequence

command is received from the CPU, auto focus, 1 track jump, 2N track jumps, and fine search are executed

automatically.

SSP (servo signal processor LSI) is used in an exclusive manner during the auto sequence execution (when

XBUSY = low), so that commands from the CPU are not transferred to the SSP, but can be sent to the

CXD2510Q.

In addition, when using the auto sequence, connect the CPU, RF and SSP as shown in Fig. 3-7, and turn the

A.SEQ of register 9 on.

When CLOK goes from low to high while XBUSY is low, XBUSY does not become high for a maximum of

100μs after that point. This is designed to prevent the transfer of erroneous data to the SSP when XBUSY

changes from low to high by the monostable multivibrator, which is reset by CLOK being low (when XBUSY

is low).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CXD2529Q | CD Digital Signal Processor |

| CXD2540Q-2 | CD DIGITAL SIGNAL PROCESSOR |

| CXD2548 | CD Digital Signal Processor with Built-in Digital Servo and DAC |

| CXD2548R | CD Digital Signal Processor with Built-in Digital Servo and DAC |

| CXD2552 | 1 BIT D/A CONVERTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CXD2512R | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:C-MOS ESP CONTROLLER FOR CD |

| CXD2513AR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:C-MOS ELECTRONIC ZOOMING/ELECTRICAL IMAGE STABILIZER |

| CXD2515Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:C-MOS CD DIGITAL PROCESSOR WITH SERVO |

| CXD2525AQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CD-Player Decoder |

| CXD2525AR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CD-Player Decoder |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。