- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378482 > CY28341-2 (Cypress Semiconductor Corp.) Universal Clock Chip for VIA P4M/KT/KM400 DDR Systems PDF資料下載

參數(shù)資料

| 型號(hào): | CY28341-2 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | Universal Clock Chip for VIA P4M/KT/KM400 DDR Systems |

| 中文描述: | 通用時(shí)鐘芯片的威盛P4M/KT/KM400的DDR系統(tǒng) |

| 文件頁(yè)數(shù): | 8/19頁(yè) |

| 文件大?。?/td> | 174K |

| 代理商: | CY28341-2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

CY28341-2

Document #: 38-07471 Rev. *B

Page 8 of 19

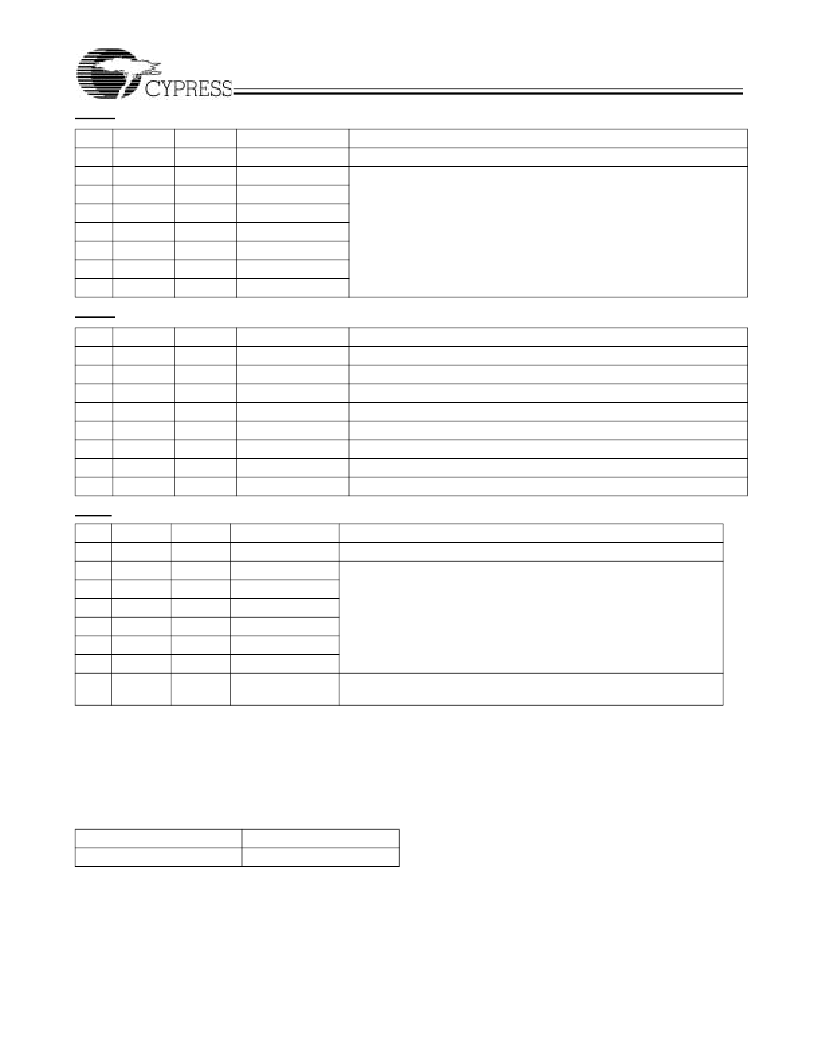

Dial-a-Frequency Feature

SMBus Dial-a-Frequency feature is available in this device via

Byte7 and Byte9.

P is a PLL constant that depends on the frequency selection

prior to accessing the Dial-a-Frequency feature.

Byte 7: Dial-a-Frequency Control Register N

Bit

7

6

5

4

3

2

1

0

@Pup

0

0

0

0

0

0

0

0

Pin#

Name

Description

Reserved

N6, MSB

N5

N4

N3

N2

N3

N0, LSB

Reserved for device function test.

These bits are for programming the PLL’s internal N register. This access

allows the user to modify the CPU frequency at very high resolution

(accuracy). All other synchronous clocks (clocks that are generated from

the same PLL, such as PCI) remain at their existing ratios relative to the

CPU clock.

Byte 8: Silicon Signature Register (all bits are read-only)

Bit

7

6

5

4

3

2

1

0

@Pup

0

0

0

1

1

0

0

0

Pin#

Name

Description

Revision_ID3

Revision_ID2

Revision_ID1

Revision_ID0

Vendor_ID3

Vendor_ID2

Vendor_ID1

Vendor_ID0

Revision ID bit [3]

Revision ID bit [2]

Revision ID bit [1]

Revision ID bit [0]

Cypress's Vendor ID bit [3].

Cypress's Vendor ID bit [2].

Cypress's Vendor ID bit [1].

Cypress's Vendor ID bit [0].

Byte9: Dial-A-Frequency Control Register R

Bit

7

6

5

4

3

2

1

@Pup

0

0

0

0

0

0

0

Pin#

Name

Description

Reserved

These bits are for programming the PLL’s internal R register. This access

allows the user to modify the CPU frequency at very high resolution

(accuracy). All other synchronous clocks (clocks that are generated from

the same PLL, such as PCI) remain at their existing ratios relative to the

CPU clock.

R5, MSB

R4

R3

R2

R1

R0

0

0

DAF_ENB

R and N register mux selection. 0 = R and N values come from the ROM.

1 = data is load from DAF (SMBus) registers.

Table 8.

FS(4:0)

P

XXXXX

96016000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY29962 | 2.5V/3.3V, 150-MHz Multi-Output Zero Delay Buffer |

| CY30 | Sensor interface for an inductive engine wheel speed single rotation sensor |

| CY37128V | 5V, 3.3V, ISR⑩ High-Performance CPLDs |

| CY37256V | 5V, 3.3V, ISR⑩ High-Performance CPLDs |

| CY54FCT138CTDMB | 1-of-8 Decoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY28341-2_05 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Clock Chip for VIA⑩P4M/KT/KM400 DDR Systems |

| CY28341-3 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Clock Chip for VIA⑩P4M/KT/KM400A DDR Systems |

| CY28341OC | 制造商:Rochester Electronics LLC 功能描述:FTG FOR VIA P4 CHIPSET - Bulk |

| CY28341OC-2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY28341OC-2T | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Clock Chip for VIA⑩P4M/KT/KM400 DDR Systems |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。