- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄170345 > CY38050V256-125BBI (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 10 ns, PBGA256 PDF資料下載

參數(shù)資料

| 型號(hào): | CY38050V256-125BBI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, 10 ns, PBGA256 |

| 封裝: | 17 X 17 MM, FBGA-256 |

| 文件頁數(shù): | 40/45頁 |

| 文件大小: | 720K |

| 代理商: | CY38050V256-125BBI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. *G

Page 45 of 45

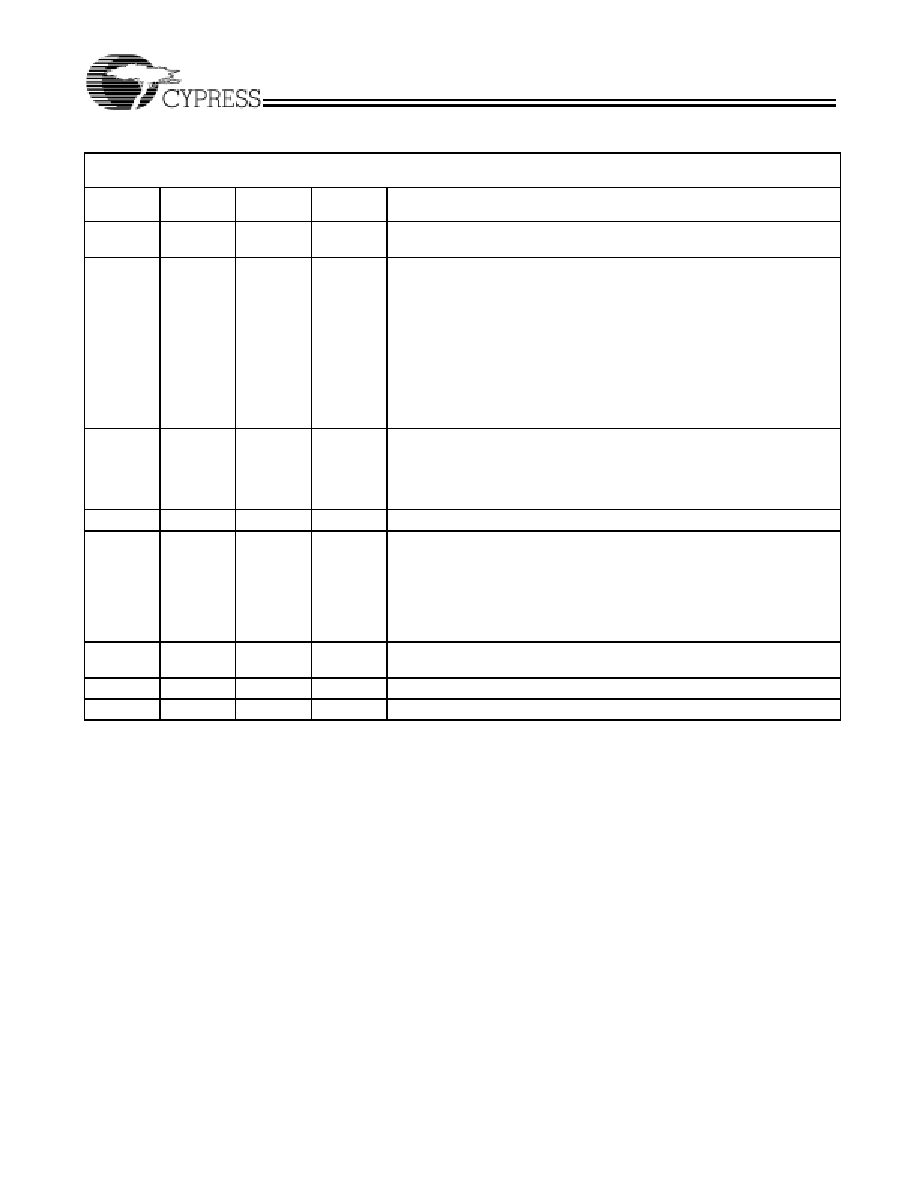

Document History Page

Document Title: Quantum38K ISR CPLDs Designed for Migration

Document Number: 38-03043

REV.

ECN NO.

Issue

Date

Orig. of

Change

Description of Change

**

106747

04/25/01

SZV

New Data Sheet

Convert from Spec number 38-01058 to 38-03043

*A

108380

07/19/01

RN

Deleted 38K15 device from the data sheet.

Deleted 144FBGA package from the data sheet.

Changed ESD spec from “MIL-STD-883” to “JEDEC EIA./JESD22-A114-A“.

Changed the two bin offerings for all devices from “83 MHz and 66 MHz” to

“125 MHz and 83 MHz” respectively

Changed the timing specs accordingly

Changed the part ordering information accordingly

Added paragraph about Quantum38K being CompactPCI hot swap Ready.

Updated I/O standard Timing Delay Specs and changed the default I/O

standard from 3.3V PCI to LVCMOS.

Added Standby ICC Spec

*B

109680

09/25/01

RN

Removed revision ‘B’ from CY38K100 part number

Removed errata from CY38K100 devices, as it is no longer applicable

208-pin package will now be “Thermally Enhanced Quad Flat Pack”

(208-EQFP) instead of Plastic Quad Flat Pack (PQFP) for better heat dissi-

pation and power management

*C

111959

12/21/01

RN

Combine with spec# 38-04042

*D

112947

04/23/02

RN

Updated pinouts for Quantum38K30 and Quantum38K50 packages

Updated Standby current (ICC0) spec on page 13

Added a section titled “Family, Package and Density Migration in

Quantum38K CPLDs” on page 10

Added slow slew rate timing delay adjustments to table on page 18

Added Table 3 on page 28 identifying bank assignments of global

control/clock signals

*E

117519

09/17/02

OOR

Changed data sheet status from Preliminary to Final

Added note #4 to DC Characteristics (p.12)

*F

122239

12/28/02

RBI

Power up requirements added to Operating Range Information

*G

125910

04/22/03

OOR

Added note to title page: “Use Delta39K CPLD For All New Designs”

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY38050V484-125BBC | LOADABLE PLD, 10 ns, PBGA484 |

| CY38050V484-125BBI | LOADABLE PLD, 10 ns, PBGA484 |

| CY39030Z144-222BBC | LOADABLE PLD, 7 ns, PBGA144 |

| CY39030Z144-83BBC | LOADABLE PLD, 15 ns, PBGA144 |

| CY39030Z144-83BBI | LOADABLE PLD, 15 ns, PBGA144 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

| CY3858-000 | 制造商:TE Connectivity 功能描述:2524F0524-1L/9-9-L016 - Cable Rools/Shrink Tubing |

| CY39 | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Crystals |

| CY3900I | 功能描述:開發(fā)軟件 ISR Programming Kit RoHS:否 制造商:Atollic Inc. 產(chǎn)品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CY3900I_05 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Delta39K⑩⁄Ultra37000⑩ ISR⑩ Programming Kits |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。