- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄170345 > CY38050V484-83BBC (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 15 ns, PBGA484 PDF資料下載

參數(shù)資料

| 型號(hào): | CY38050V484-83BBC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, 15 ns, PBGA484 |

| 封裝: | 1 MM PITCH, FBGA-484 |

| 文件頁數(shù): | 42/45頁 |

| 文件大小: | 720K |

| 代理商: | CY38050V484-83BBC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當(dāng)前第42頁第43頁第44頁第45頁

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. *G

Page 6 of 45

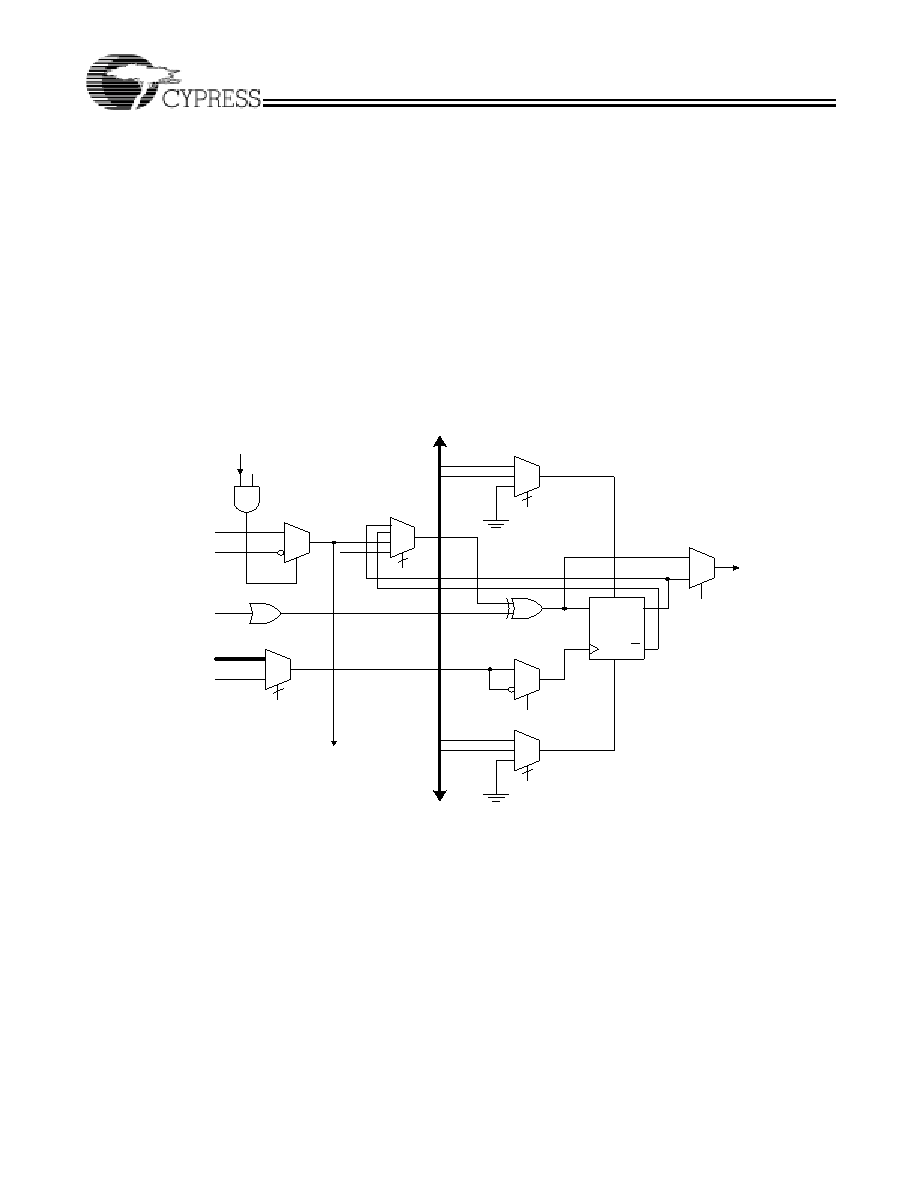

implement adders, subtractors, magnitude comparators,

parity tree, or even generic XOR logic. The output of the

macrocell is either registered or combinatorial.

Carry Chain Logic

The Quantum38K macrocell features carry chain logic which

is used for fast and efficient implementation of arithmetic

operations. The carry logic connects macrocells in up to four

logic blocks for a total of 64 macrocells. Effective data path

operations are implemented through the use of carry-in arith-

metic, which drives through the circuit quickly. Figure 4 shows

that the carry chain logic within the macrocell consists of two

product terms (CPT0 and CPT1) from the PTA and an input

carry-in for carry logic. The inputs to the carry chain mux are

connected directly to the product terms in the PTA. The output

of the carry chain mux generates the carry-out for the next

macrocell in the logic block as well as the local carry input that

is connected to an input of the XOR input mux. Carry-in and a

configuration bit are inputs to an AND gate. This AND gate

provides a method of segmenting the carry chain in any

macrocell in the logic block.

Macrocell Clocks

Clocking of the register is highly flexible. Four global

synchronous clocks (GCLK[3:0]) and a Product Term clock

(PTCLK)

are

available

at

each

macrocell

register.

Furthermore, a clock polarity mux within each macrocell

allows the register to be clocked on the rising or the falling

edge (see macrocell diagram in Figure 4).

PRESET/RESET Configurations

The macrocell register can be asynchronously preset and

reset using the PRESET and RESET mux. Both signals are

active high and can be controlled by either of two Preset/Reset

product terms (PRC[1:0] in Figure 4) or GND. In situations

where the PRESET and RESET are active at the same time,

RESET takes priority over PRESET.

Figure 4. Quantum38K Macrocell

D

Q

PSET

RES

GCLK[3:0]

PTCLK

FROM PTM

CPT0

CPT1

P

R

C

[1:0]

0

1

0

1

To PIM

C

Carry Out

(to macrocell n+1)

Carry In

(from macrocell n-1)

Up To 16 PTs

PRESET

Mux

Clock

Polarity

Mux

RESET

Mux

Clock Mux

Carry Chain

Mux

XOR Input

Mux

Output Mux

Q

C

3

2

3

C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY38050V208-125NC | LOADABLE PLD, 10 ns, PQFP208 |

| CY38050V208-125NI | LOADABLE PLD, 10 ns, PQFP208 |

| CY38050V256-125BBC | LOADABLE PLD, 10 ns, PBGA256 |

| CY38050V256-125BBI | LOADABLE PLD, 10 ns, PBGA256 |

| CY38050V484-125BBC | LOADABLE PLD, 10 ns, PBGA484 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

| CY3858-000 | 制造商:TE Connectivity 功能描述:2524F0524-1L/9-9-L016 - Cable Rools/Shrink Tubing |

| CY39 | 制造商:PLETRONICS 制造商全稱:Pletronics, Inc. 功能描述:Crystals |

| CY3900I | 功能描述:開發(fā)軟件 ISR Programming Kit RoHS:否 制造商:Atollic Inc. 產(chǎn)品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CY3900I_05 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Delta39K⑩⁄Ultra37000⑩ ISR⑩ Programming Kits |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。