- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376786 > DM74LS109AM (FAIRCHILD SEMICONDUCTOR CORP) Dual Positive-Edge-Triggered J-K Flip-Flop with Preset, Clear, and Complementary Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | DM74LS109AM |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Dual Positive-Edge-Triggered J-K Flip-Flop with Preset, Clear, and Complementary Outputs |

| 中文描述: | LS SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO16 |

| 封裝: | 0.150 INCH, MS-012, SOIC-16 |

| 文件頁數(shù): | 3/5頁 |

| 文件大小: | 52K |

| 代理商: | DM74LS109AM |

3

www.fairchildsemi.com

D

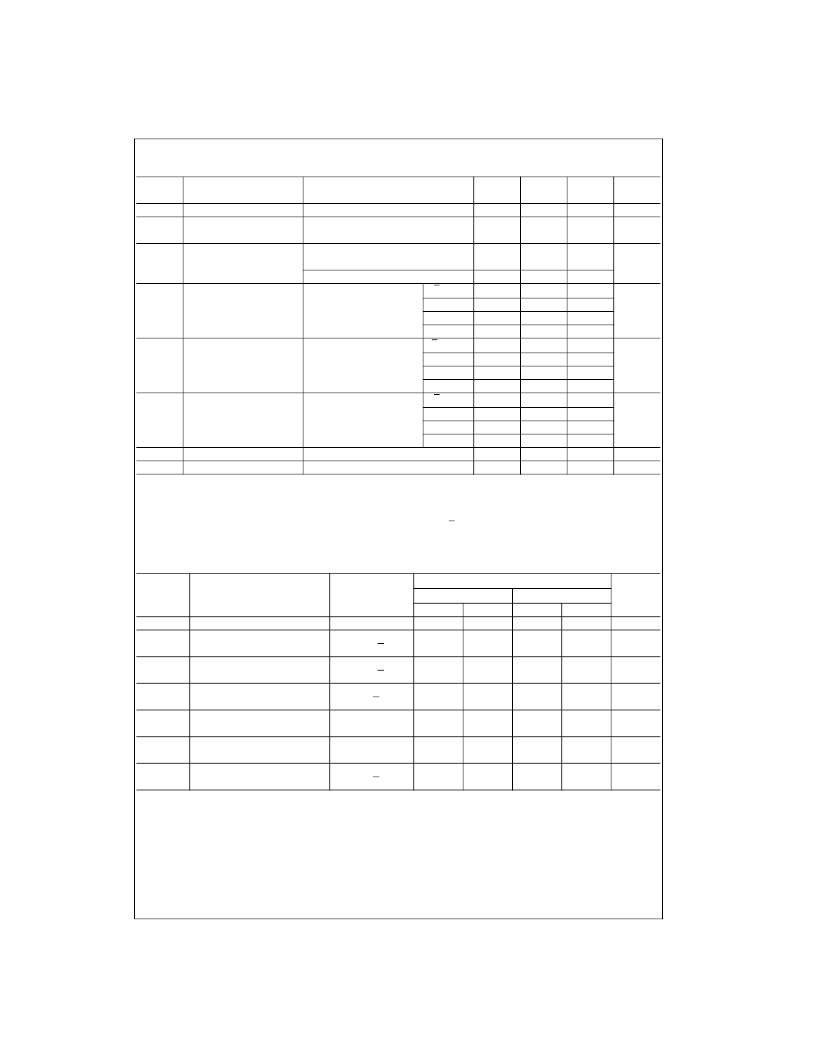

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Note 7:

All typicals are at V

CC

=

5V, T

A

=

25

°

C.

Note 8:

Not more than one output should be shorted at a time, and the duration should not exceed one second. For devices, with feedback from the outputs,

where shorting the outputs to ground may cause the outputs to change logic state an equivalent test may be performed where V

O

=

2.125V with the minimum

and maximum limits reduced by one half from their stated values. This is very useful when using automatic test equipment.

Note 9:

I

CC

is measured with all outputs OPEN, with CLOCK grounded after setting the Q and Q outputs HIGH in turn.

Switching Characteristics

at V

CC

=

5V and T

A

=

25

°

C

Symbol

Parameter

Conditions

Min

Typ

Max

Units

(Note 7)

V

I

V

OH

Input Clamp Voltage

HIGH Level

Output Voltage

V

CC

=

Min, I

I

=

18 mA

V

CC

=

Min, I

OH

=

Max

V

IL

=

Max, V

IH

=

Min

V

CC

=

Min, I

OL

=

Max

V

IL

=

Max, V

IH

=

Min

I

OL

=

4 mA, V

CC

=

Min

V

CC

=

Max

V

I

=

7V

1.5

V

2.7

3.4

V

V

OL

LOW Level

Output Voltage

0.35

0.5

V

0.25

0.4

I

I

Input Current @ Max

Input Voltage

J, K

Clock

0.1

0.1

mA

Preset

Clear

0.2

0.2

I

IH

HIGH Level

Input Current

V

CC

=

Max

V

I

=

2.7V

J,K

Clock

Preset

20

20

40

μ

A

Clear

40

I

IL

LOW Level

V

CC

=

Max

V

I

=

0.4V

J, K

0.4

0.4

0.8

0.8

100

8

Input Current

Clock

Preset

Clear

mA

I

OS

I

CC

Short Circuit Output Current

Supply Current

V

CC

=

Max (Note 8)

V

CC

=

Max (Note 9)

20

mA

mA

4

From (Input)

R

L

=

2 k

Symbol

Parameter

To (Output)

C

L

=

15 pF

Min

25

C

L

=

50 pF

Min

20

Units

Max

Max

f

MAX

t

PLH

Maximum Clock Frequency

Propagation Delay Time

LOW-to-HIGH Level Output

MHz

Clock to

Q or Q

25

35

ns

t

PHL

Propagation Delay Time

HIGH-to-LOW Level Output

Propagation Delay Time

Clock to

Q or Q

Clear

30

35

ns

t

PLH

25

35

ns

LOW-to-HIGH Level Output

Propagation Delay Time

HIGH-to-LOW Level Output

to Q

Clear

to Q

t

PHL

30

35

ns

t

PLH

Propagation Delay Time

LOW-to-HIGH Level Output

Propagation Delay Time

Preset

to Q

Preset

25

35

ns

t

PHL

30

35

ns

HIGH-to-LOW Level Output

to Q

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM74LS109AN | Dual Positive-Edge-Triggered J-K Flip-Flop with Preset, Clear, and Complementary Outputs |

| DM74LS109AMX | J-K-Type Flip-Flop |

| DM74LS10M | Triple 3-Input NAND Gate |

| DM74LS10 | Triple 3-Input NAND Gate(三3輸入與非門) |

| DM74LS10N | Triple 3-Input NAND Gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM74LS109AMX | 功能描述:觸發(fā)器 Dl J-K Flip-Flop RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| DM74LS109AN | 功能描述:觸發(fā)器 Dl J-K Flip-Flop RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| DM74LS109AN83 | 制造商:National Semiconductor 功能描述:74LS109N |

| DM74LS10M | 功能描述:邏輯門 Trp 3-Input NAND Gat RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| DM74LS10MX | 功能描述:邏輯門 Trp 3-Input NAND Gat RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。