- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377001 > DSP56857BUE (飛思卡爾半導(dǎo)體(中國)有限公司) 16-bit Digital Signal Controllers PDF資料下載

參數(shù)資料

| 型號: | DSP56857BUE |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | 16-bit Digital Signal Controllers |

| 中文描述: | 16位數(shù)字信號控制器 |

| 文件頁數(shù): | 15/53頁 |

| 文件大小: | 680K |

| 代理商: | DSP56857BUE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

Introduction

56857 Technical Data, Rev. 6

Freescale Semiconductor

15

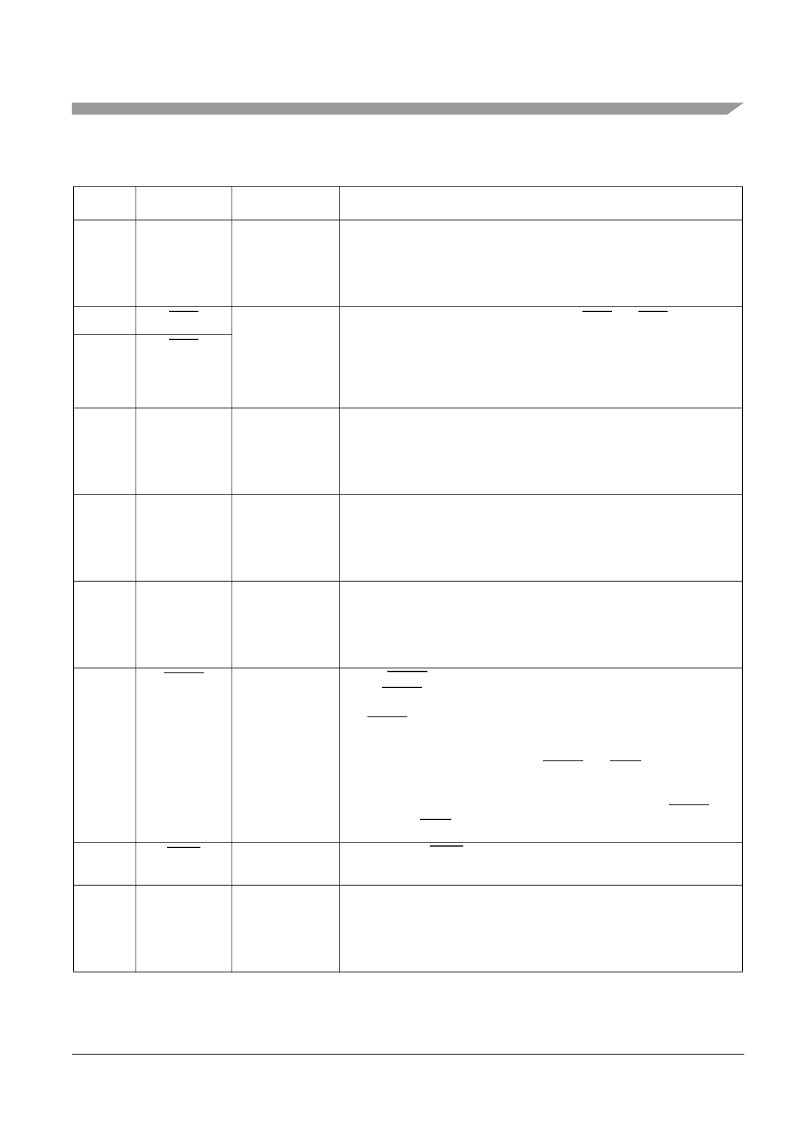

77

TIO3

GPIOG3

Input

/Output

Input/Output

Timer Input/Output (TIO3)

—This pin can be independently configured to

be either a timer input source or an output flag.

Port G GPIO (3)

—This pin is a General Purpose I/O (GPIO) pin that can

individually be programmed as an input or output pin.

15

IRQA

Input

External Interrupt Request A and B

—The IRQA and IRQB inputs are

asynchronous external interrupt requests that indicate that an external

device is requesting service. A Schmitt trigger input is used for noise

immunity. They can be programmed to be level-sensitive or

negative-edge- triggered. If level-sensitive triggering is selected, an

external pull-up resistor is required for Wired-OR operation.

16

IRQB

10

MODE A

GPIOH0

Input

Input/Output

Mode Select (MODE A)

—During the bootstrap process MODE A selects

one of the eight bootstrap modes.

Port H GPIO (0)

—This pin is a General Purpose I/O (GPIO) pin after the

bootstrap process has completed.

11

MODE B

GPIOH1

Input

Input/Output

Mode Select (MODE B)

—During the bootstrap process MODE B selects

one of the eight bootstrap modes.

Port H GPIOH1

—This pin is a General Purpose I/O (GPIO) pin after the

bootstrap process has completed.

12

MODE C

GPIOH2

Input

Input/Output

Mode Select (MODE C)

—During the bootstrap process MODE C selects

one of the eight bootstrap modes.

Port H GPIO (2)

—This pin is a General Purpose I/O (GPIO) pin after the

bootstrap process has completed.

28

RESET

Input

Reset (RESET)

—This input is a direct hardware reset on the processor.

When RESET is asserted low, the controller is initialized and placed in

the Reset state. A Schmitt trigger input is used for noise immunity. When

the RESET pin is deasserted, the initial chip operating mode is latched

from the MODE A, MODE B, and MODE C pins.

To ensure complete hardware reset, RESET and TRST should be

asserted together. The only exception occurs in a debugging

environment when a hardware reset is required and it is necessary not to

reset the JTAG/Enhanced OnCE module. In this case, assert RESET, but

do not assert TRST.

27

RSTO

Output

Reset Output (RSTO)

—This output is asserted on any reset condition

(external reset, low voltage, software or COP).

51

RXD0

GPIOE0

Input

Input/Output

Serial Receive Data 0 (RXD0)

—This input receives byte-oriented serial

data and transfers it to the SCI 0 receive shift register.

Port E GPIO (0)

—This pin is a General Purpose I/O (GPIO) pin that can

individually be programmed as input or output pin.

Table 3-1 56857 Signal and Package Information for the 100-pin LQFP (Continued)

Pin No.

Signal Name

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSP56857E | 16-bit Digital Signal Controllers |

| DSP56858E | 16-bit Digital Signal Controllers |

| DSP56858FV120 | 16-bit Digital Signal Controllers |

| DSP56858FVE | 16-bit Digital Signal Controllers |

| DSP56858VF120 | 16-bit Digital Signal Controllers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSP56857E | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| DSP56857PB | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:120 MIPS Hybrid Processor |

| DSP56858 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| DSP56858E | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| DSP56858EVM | 制造商:Freescale Semiconductor 功能描述:Microprocessor Support IC For Use With:D |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。