- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377008 > DT28F320S3-120 (Intel Corp.) 16 Characters x 2 Lines, 5x7 Dot Matrix Character and Cursor PDF資料下載

參數(shù)資料

| 型號(hào): | DT28F320S3-120 |

| 廠商: | Intel Corp. |

| 英文描述: | 16 Characters x 2 Lines, 5x7 Dot Matrix Character and Cursor |

| 中文描述: | 字寬FlashFile⑩Memory系列 |

| 文件頁數(shù): | 7/52頁 |

| 文件大小: | 1262K |

| 代理商: | DT28F320S3-120 |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

E

28F160S3, 28F320S3

7

ADVANCE INFORMATION

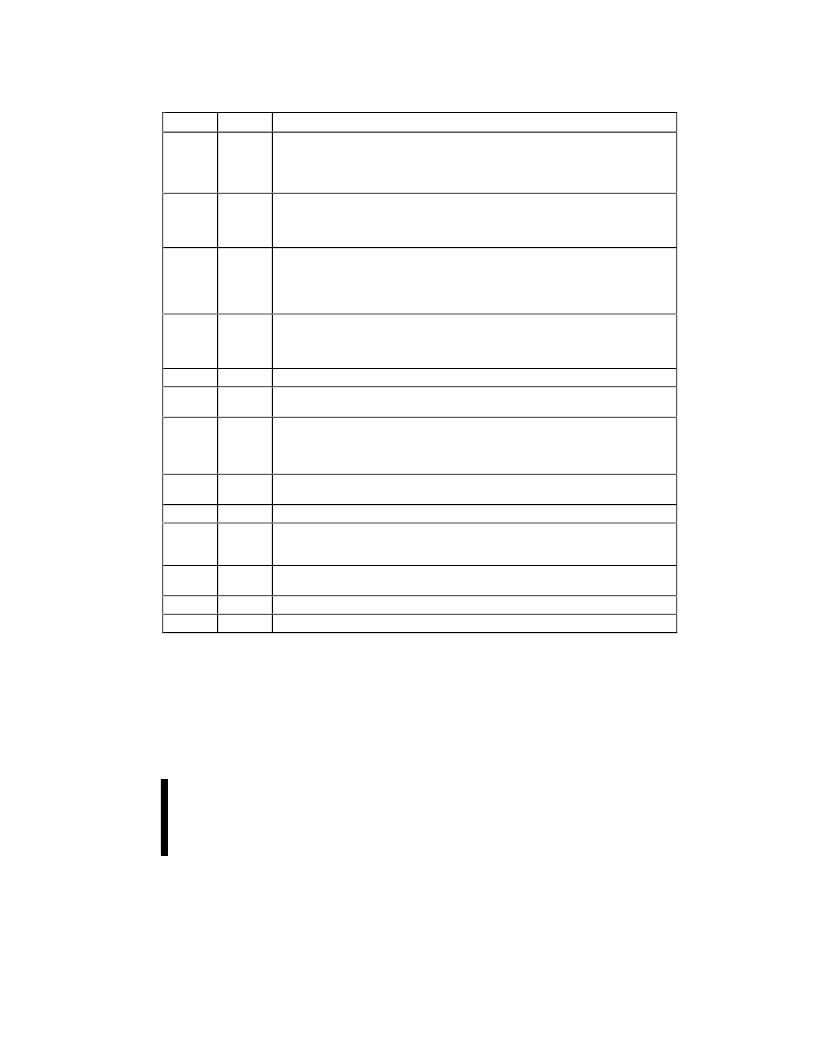

Table 1. Pin Descriptions

Sym

Type

Name and Function

A

0

–A

21

INPUT

ADDRESS INPUTS:

Address inputs for read and write operations are internally

latched during a write cycle. A

0

selects high or low byte when operating in x8 mode.

In x16 mode, A

0

is not used; input buffer is off.

16-Mbit

→

A

0

–A

20

32-Mbit

→

A

0

–A

21

DATA INPUTS/OUTPUTS:

Inputs data and commands during CUI write cycles;

outputs data during memory array, Status Register, query and identifier code read

cycles. Data pins float to high-impedance when the chip is deselected or outputs

are disabled. Data is internally latched during a write cycle.

DQ

0

–

DQ

15

INPUT/

OUTPUT

CE

0

#,

CE

1

#

INPUT

CHIP ENABLE:

Activates the device’s control logic, input buffers, decoders, and

sense amplifiers. With CE

0

# or CE

1

# high, the device is deselected and power

consumption reduces to standby levels. Both CE

0

# and CE

1

# must be low to select

the device. Device selection occurs with the latter falling edge of CE

0

# or CE

1

#. The

first rising edge of CE

0

# or CE

1

# disables the device.

RESET/DEEP POWER-DOWN:

When driven low, RP# inhibits write operations

which provides data protection during system power transitions, puts the device in

deep power-down mode, and resets internal automation. RP#-high enables normal

operation. Exit from deep power-down sets the device to read array mode.

RP#

INPUT

OE#

INPUT

OUTPUT ENABLE:

Gates the device’s outputs during a read cycle.

WE#

INPUT

WRITE ENABLE:

Controls writes to the CUI and array blocks. Addresses and data

are latched on the rising edge of the WE# pulse.

STS

OPEN

DRAIN

OUTPUT

STATUS:

Indicates the status of the internal state machine. When configured in

level mode (default), it acts as a RY/BY# pin. For this and alternate configurations

of the STATUS pin, see the Configuration command. Tie STS to V

CC

with a pull-up

resistor.

WP#

INPUT

WRITE PROTECT:

Master control for block locking. When V

IL

, locked blocks

cannot be erased or programmed, and block lock-bits cannot be set or cleared.

BYTE#

INPUT

BYTE ENABLE:

Configures x8 mode (low) or x16 mode (high).

V

PP

SUPPLY

BLOCK ERASE, PROGRAM, LOCK-BIT CONFIGURATION POWER SUPPLY:

Necessary voltage to perform block erase, program, and lock-bit configuration

operations. Do not float any power pins.

V

CC

SUPPLY

DEVICE POWER SUPPLY:

Do not float any power pins. Do not attempt block

erase, program, or block-lock configuration with invalid V

CC

values.

SUPPLY

GROUND:

Do not float any ground pins.

GND

NC

NO CONNECT:

Lead is not internally connected; it may be driven or floated.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DT28F160S3-120 | 16 Characters x 2 Lines, 5x7 Dot Matrix Character and Cursor |

| dt31-2025at | Telecommunication HDSL Transformer |

| DT31-2026AT | Telecommunication HDSL Transformer |

| DT31-2031AT | Telecommunication HDSL Transformer |

| DT31-2032AT | Telecommunication HDSL Transformer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DT28F320S3-140 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:WORD-WIDE FlashFile MEMORY FAMILY |

| DT28F640J5-150 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM|FLASH|4MX16/8MX8|CMOS|SOP|56PIN|PLASTIC |

| DT28F640J5A-150 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:5 Volt Intel StrataFlash? Memory |

| DT28F800F3B120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:FAST BOOT BLOCK FLASH MEMORY FAMILY 8 AND 16 MBIT |

| DT28F800F3B95 | 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。