- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384279 > EDE2104ABSE-5C-E (ELPIDA MEMORY INC) 2G bits DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號: | EDE2104ABSE-5C-E |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | 2G bits DDR2 SDRAM |

| 中文描述: | 512M X 4 DDR DRAM, 0.5 ns, PBGA68 |

| 封裝: | ROHS COMPLIANT, FBGA-68 |

| 文件頁數(shù): | 17/81頁 |

| 文件大小: | 604K |

| 代理商: | EDE2104ABSE-5C-E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁

EDE2104ABSE, EDE2108ABSE

Preliminary Data Sheet E1196E10 (Ver. 1.0)

17

-5C

Speed bin

DDR2-533 (4-4-4)

Parameter

Symbol

min.

max.

Unit

Notes

Active bank A to active bank B command period

tRRD

7.5

ns

Four active window period

tFAW

37.5

ns

/CAS to /CAS command delay

tCCD

2

tCK

Write recovery time

tWR

15

WR +

RU(tRP/tCK)

7.5

ns

Auto precharge write recovery + precharge time

tDAL

tCK

1, 9

Internal write to read command delay

tWTR

ns

Internal read to precharge command delay

tRTP

7.5

ns

Exit self-refresh to a non-read command

tXSNR

tRFC + 10

ns

Exit self-refresh to a read command

tXSRD

200

tCK

Exit precharge power-down to any non-read command

tXP

2

tCK

Exit active power-down to read command

Exit active power-down to read command

(slow exit/low power mode)

CKE minimum pulse width (high and low pulse width)

tXARD

2

tCK

3

tXARDS

6

AL

tCK

2, 3

tCKE

3

tCK

Output impedance test driver delay

tOIT

0

12

ns

MRS command to ODT update delay

t

MOD

0

12

ns

Auto-refresh to active/auto-refresh command time

Average periodic refresh interval

(0

°

C

≤

TC

≤

+85

°

C)

(+85

°

C

<

TC

≤

+95

°

C)

Minimum time clocks remains ON after CKE

asynchronously drops low

Notes: 1. For each of the terms above, if not already an integer, round to the next higher integer.

2. AL: Additive Latency.

3. MRS A12 bit defines which active power-down exit timing to be applied.

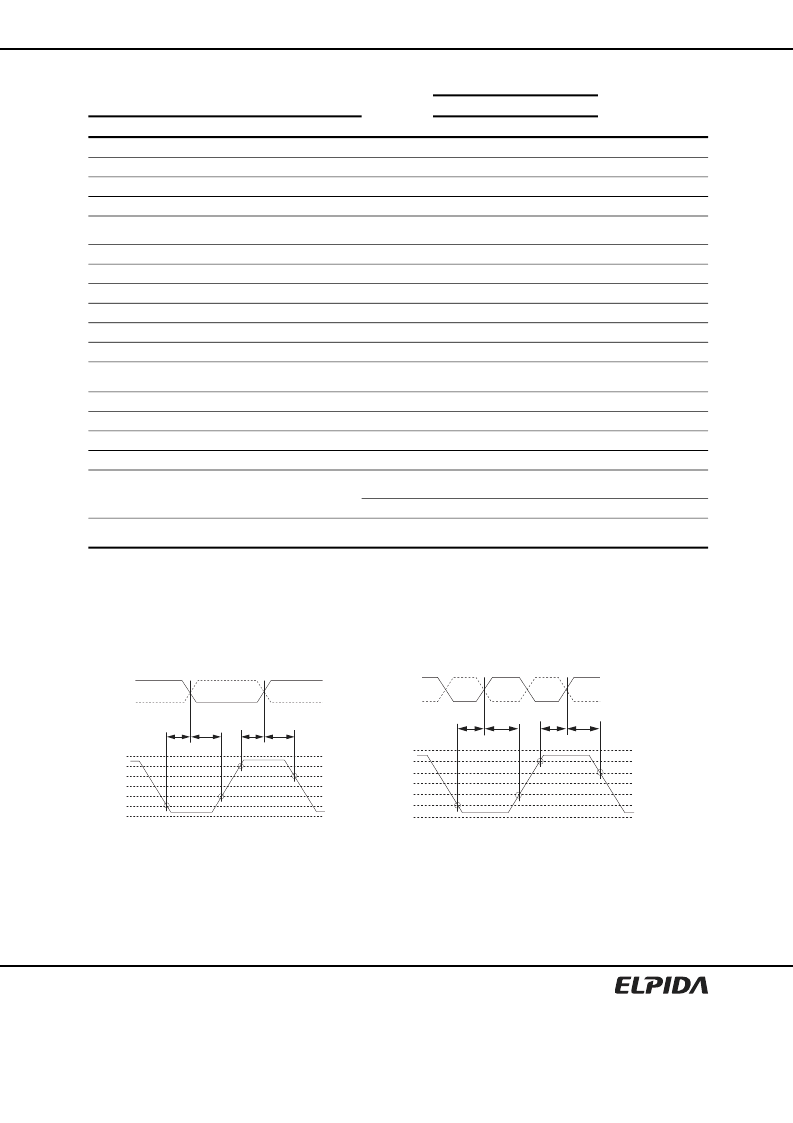

4. The figures of Input Waveform Timing 1 and 2 are referenced from the input signal crossing at the

VIH(AC) level for a rising signal and VIL(AC) for a falling signal applied to the device under test.

5. The figures of Input Waveform Timing 1 and 2 are referenced from the input signal crossing at the

VIL(DC) level for a rising signal and VIH(DC) for a falling signal applied to the device under test.

tRFC

195

ns

tREFI

7.8

μ

s

tREFI

3.9

μ

s

tDELAY

tIS + tCK + tIH

ns

DQS

/DQS

tDS

tDH

tDS

tDH

VDDQ

VIH (AC)(min.)

VIH (DC)(min.)

VREF

VIL (DC)(max.)

VIL (AC)(max.)

VSS

CK

/CK

tIS

tIH

tIS

tIH

VDDQ

VIH (AC)(min.)

VIH (DC)(min.)

VREF

VIL (DC)(max.)

VIL (AC)(max.)

VSS

Input Waveform Timing 1 (tDS, tDH)

Input Waveform Timing 2 (tIS, tIH)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EDE2104ABSE-6E-E | 2G bits DDR2 SDRAM |

| EDE2104ABSE-8G-E | 2G bits DDR2 SDRAM |

| EDE2108ABSE | 2G bits DDR2 SDRAM |

| EDE2108ABSE-5C-E | 2G bits DDR2 SDRAM |

| EDE2108ABSE-6E-E | 2G bits DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EDE2104ABSE-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:2G bits DDR2 SDRAM |

| EDE2104ABSE-8G-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:2G bits DDR2 SDRAM |

| EDE2108ABSE | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:2G bits DDR2 SDRAM |

| EDE2108ABSE-5C-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:2G bits DDR2 SDRAM |

| EDE2108ABSE-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:2G bits DDR2 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。