- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362688 > EM78P468N (ELAN Microelctronics Corp .) 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | EM78P468N |

| 廠商: | ELAN Microelctronics Corp . |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-BIT MICROCONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁(yè)數(shù): | 15/82頁(yè) |

| 文件大小: | 1491K |

| 代理商: | EM78P468N |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

EM78P468N

8-BIT Microcontroller

A1

Product Specification

(V1.2) 03.15.2005

(This specification is subject to change without further notice)

11

1

A10

A9

A8

A7

~

A0

R3

PC

CAL

RET

RETL

RETI

L

00 PAGE0 0

03FF

000~

01 PAGE1 0400~07FF

10 PAGE2 0800~0BFF

11 PAGE3 0C00~0FFF

STACK LEVEL 1

STACK LEVEL 2

STACK LEVEL 3

STACK LEVEL 4

STACK LEVEL 5

STACK LEVEL 6

STACK LEVEL 7

STACK LEVEL 8

Reset vector

000H

TCC overfl

errupt vector

ow nt

003H

Exteral INT

nterrupt vecto

0 pin

r

006H

Exteral INT1 pin nterrupt vector

Counter 1 underflow interrupt vector

Counter 2 underflow interrupt vector

high pulse width timer underflow interrupt vector

low pulse width timer underflow interrupt vector

Port 6,Port8 pin change wake-up interrupt vector

009H

00CH

00FH

012H

015H

018H

On-Chip Program memory

FFFH

U

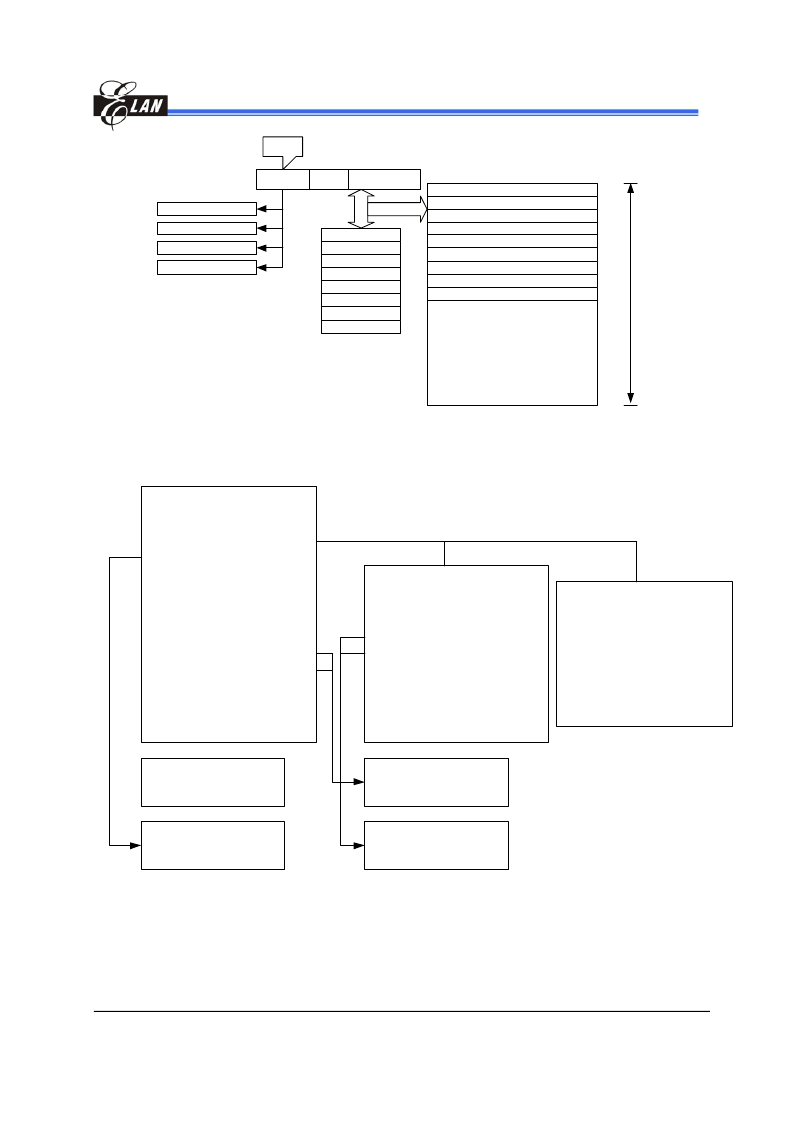

Fig. 3 Program Counter Organization

ADDRESS

0 0

0 1

0 2

0 3

0 4

0 5

0 6

0 7

0 8

0 9

0 A

0 B

0 C

0 D

0 E

0 F

IAR (Indirect Addressing Register)

lock Counter)

Counter)

TCC (Time C

PC (Program

SR (Status R

RSR (RAM s

PORT5 (Port

PORT6 (Port6 I/O data register)

PORT7 (Port7

PORT8 (Por

LCDCR (LC

LCD_ADDR

LCD_DB (L

CNTER (Cou

)

SBPCR (Sy

IRCR (IR, Pin of IR;INT0/1;TCC control)

ISR (interrup

R5 bit 0 -> 0

control register page 0

R5 bit 0 -> 1

control register page 1

egister)

elect register)

5 & IOCPAGE Control)

I/O data register)

t8 I/O data register)

D control register)

(LCD address)

CD data buffer)

nter enable register

stem, Booster , PLL control)

t status register)

16 byte

1 0

|

1 F

common register

ban

32 byte common register

2 0

|

3 F

ort5 I/O & LCD segment control)

P5CR (P

P6CR (Port6 I/O c

l register)

R (Port7 I/O c

ol register)

(Port8 I/O c

l register)

_ADDR (128

RAM address)

byte

RAM_DB (128 by

M data buffer)

te RA

CNT1PR (Counter

eset register)

CNT2PR (Counter

eset register)

HPWTPR (High-p

width timer preset)

ulse

LPWTPR (Low-pulse width timer preset)

ontro

P7C

P8CR

ontr

ontro

RAM

1 pr

2 pr

IMR (interrupt mask register)

k 0 ~ bank 3

128 byte data RAM

LCD RAM 4*32 bits

CNT12CR (Counter 1,2 control register)

6PH (Port 6 pull-high control register)

P

6OD (Port 6 open drain control register)

P

control register)

P6PL (Port 6 pull-low control register)

WUCR

nk current)

TCCCR

rol register)

DTCR (WDT control register)

W

LPWTCR (high/low pulse width timer control)

Mem

iguration

H

P8PH (Port 8 pull-high

(Wake up & P5.7 si

(TCC & INT0 cont

ory Conf

Fig. 4 Data

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EM78P468NAQ | 8-BIT MICROCONTROLLER |

| EM78P468NBQ | 8-BIT MICROCONTROLLER |

| EM78P468NCQ | 8-BIT MICROCONTROLLER |

| EM78P468NH | 8-BIT MICROCONTROLLER |

| EM78P468NQ | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EM7A8620 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:Voice over IP |

| EM7G | 制造商:GULFSEMI 制造商全稱:Gulf Semiconductor 功能描述:ULTRAFAST EFFICIENT PLASTIC SILICON RECTIFIER VOLTAGE: 1000V CURRENT: 1.0A |

| EM800 | 制造商:EDI 制造商全稱:Electronic devices inc. 功能描述:HIGH VOLTAGE HIGH CURRENT MINIATURE RECTIFIERS |

| EM8000EHP | 制造商:JDSU 制造商全稱:JDS Uniphase Corporation 功能描述:The industrya??s most compact 100 G test solution |

| EM800-DCM | 制造商:MRV 制造商全稱:MRV 功能描述:LambdaDriver Dispersion Compensation Module (EM800/1600-DCM and DCMD) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。