- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1919 > ENC624J600T-I/PT (Microchip Technology)IC ETHERNET CTRLR W/SPI 64-TQFP PDF資料下載

參數(shù)資料

| 型號: | ENC624J600T-I/PT |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 138/168頁 |

| 文件大小: | 0K |

| 描述: | IC ETHERNET CTRLR W/SPI 64-TQFP |

| 視頻文件: | Fast 100 Mbps Ethernet PICtail Plus Overview |

| 標(biāo)準(zhǔn)包裝: | 1,200 |

| 控制器類型: | 以太網(wǎng)控制器(IEEE 802.3) |

| 接口: | SPI |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 96mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 64-TQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

| 配用: | AC164132-ND - BOARD DAUGHTER PICTAIL ETHERNET |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁當(dāng)前第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

2007 Microchip Technology Inc.

DS21993C-page 69

PIC16CR7X

10.0

UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER

TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver

Transmitter (USART) module is one of the two serial

I/O modules. (USART is also known as a Serial

Communications Interface or SCI.) The USART can be

configured as a full duplex asynchronous system that

can communicate with peripheral devices, such as

CRT terminals and personal computers, or it can be

configured as a half duplex synchronous system that

can communicate with peripheral devices, such as A/D

or D/A integrated circuits, serial EEPROMs, etc.

The USART can be configured in the following modes:

Asynchronous (full duplex)

Synchronous – Master (half duplex)

Synchronous – Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be

set in order to configure pins RC6/TX/CK and

RC7/

RX/DT as the Universal Synchronous Asynchronous

Receiver Transmitter.

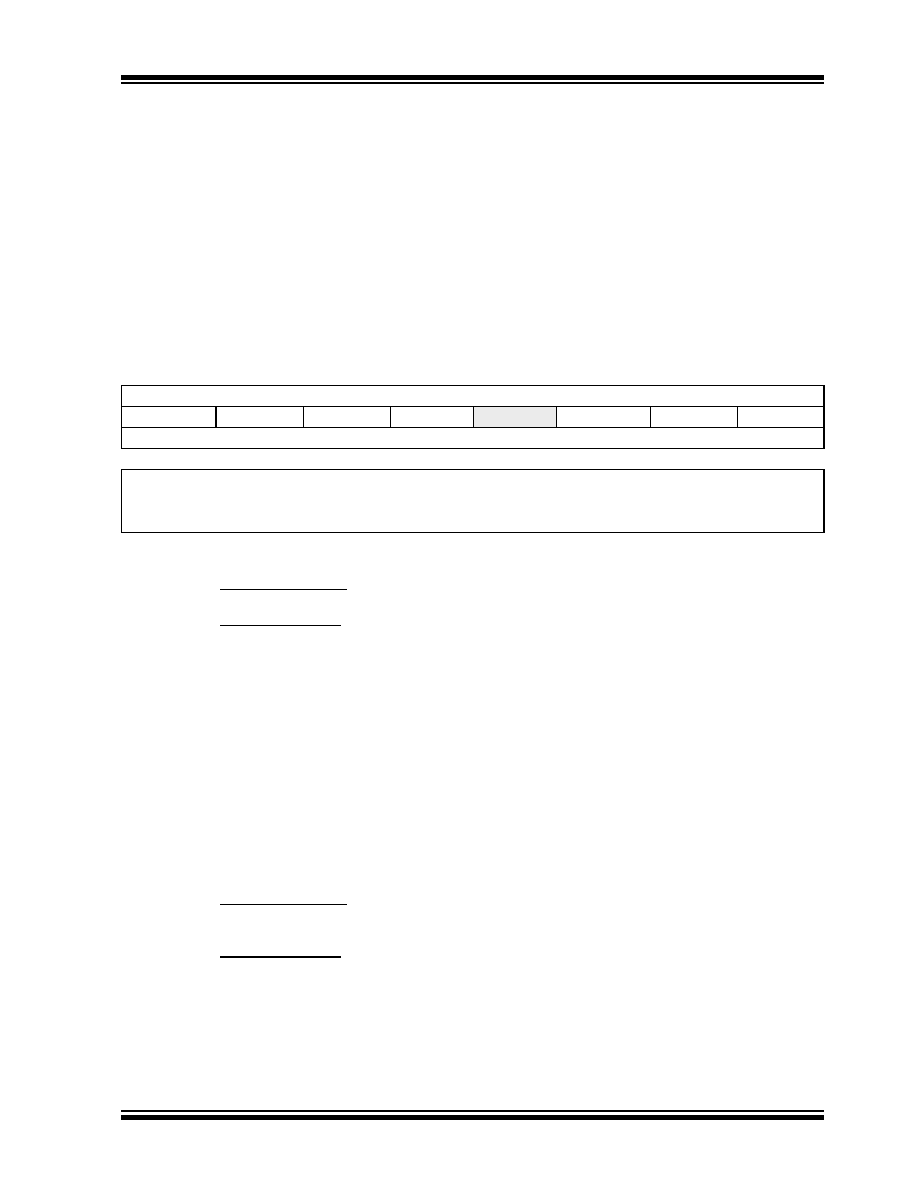

REGISTER 10-1:

TXSTA: TRANSMIT STATUS AND CONTROL (ADDRESS 98h)

R/W-0

U-0

R/W-0

R-1

R/W-0

CSRC

TX9

TXEN

SYNC

—

BRGH

TRMT

TX9D

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 7

CSRC: Clock Source Select bit

Asynchronous mode:

Don’t care

Synchronous mode:

1

= Master mode (clock generated internally from BRG)

0

= Slave mode (clock from external source)

bit 6

TX9: 9-bit Transmit Enable bit

1

= Selects 9-bit transmission

0

= Selects 8-bit transmission

bit 5

TXEN: Transmit Enable bit

1

= Transmit enabled

0

= Transmit disabled

Note:

SREN/CREN overrides TXEN in Sync mode

bit 4

SYNC: USART Mode Select bit

1

= Synchronous mode

0

= Asynchronous mode

bit 3

Unimplemented: Read as ‘0’

bit 2

BRGH: High Baud Rate Select bit

Asynchronous mode:

1

= High speed

0

= Low speed

Synchronous mode:

Unused in this mode

bit 1

TRMT: Transmit Shift Register Status bit

1

= TSR empty

0

= TSR full

bit 0

TX9D: 9th bit of Transmit Data

Can be parity bit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP1AGX90EF1152I6 | IC ARRIA GX FPGA 90K 1152FBGA |

| EP1C3T144A8N | IC CYCLONE FPGA 2910 LE 144-TQFP |

| EP1K100FC484-1N | IC ACEX 1K FPGA 100K 484-FBGA |

| EP1S80F1020C5N | IC STRATIX FPGA 80K LE 1020-FBGA |

| EP1SGX40GF1020I6 | IC STRATIX GX FPGA 40K 1020-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ENC680D05B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| ENC680D-05B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:STD MOV |

| ENC680D07B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| ENC680D-07B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:STD MOV |

| ENC680D10B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。