- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19847 > EPM7128SLC84-15 (Altera)IC MAX 7000 CPLD 128 84-PLCC PDF資料下載

參數(shù)資料

| 型號: | EPM7128SLC84-15 |

| 廠商: | Altera |

| 文件頁數(shù): | 41/66頁 |

| 文件大小: | 0K |

| 描述: | IC MAX 7000 CPLD 128 84-PLCC |

| 標(biāo)準(zhǔn)包裝: | 75 |

| 系列: | MAX® 7000 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時間 tpd(1): | 15.0ns |

| 電壓電源 - 內(nèi)部: | 4.75 V ~ 5.25 V |

| 邏輯元件/邏輯塊數(shù)目: | 8 |

| 宏單元數(shù): | 128 |

| 門數(shù): | 2500 |

| 輸入/輸出數(shù): | 68 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 84-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 84-PLCC(29.31x29.31) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 604 (CN2011-ZH PDF) |

| 其它名稱: | 544-1208-5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

46

Altera Corporation

MAX 7000 Programmable Logic Device Family Data Sheet

Notes to tables:

(1)

These values are specified under the recommended operating conditions shown in Table 14. See Figure 13 for more

information on switching waveforms.

(2)

This minimum pulse width for preset and clear applies for both global clear and array controls. The tLPA parameter

must be added to this minimum width if the clear or reset signal incorporates the tLAD parameter into the signal

path.

(3)

This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This

parameter applies for both global and array clocking.

(4)

These parameters are measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB.

(5)

The fMAX values represent the highest frequency for pipelined data.

(6)

Operating conditions: VCCIO = 3.3 V ± 10% for commercial and industrial use.

(7)

For EPM7064S-5, EPM7064S-6, EPM7128S-6, EPM7160S-6, EPM7160S-7, EPM7192S-7, and EPM7256S-7 devices,

these values are specified for a PIA fan-out of one LAB (16 macrocells). For each additional LAB fan-out in these

devices, add an additional 0.1 ns to the PIA timing value.

(8)

The tLPA parameter must be added to the tLAD, tLAC, tIC, tEN, tSEXP, tACL, and tCPPW parameters for macrocells

running in the low-power mode.

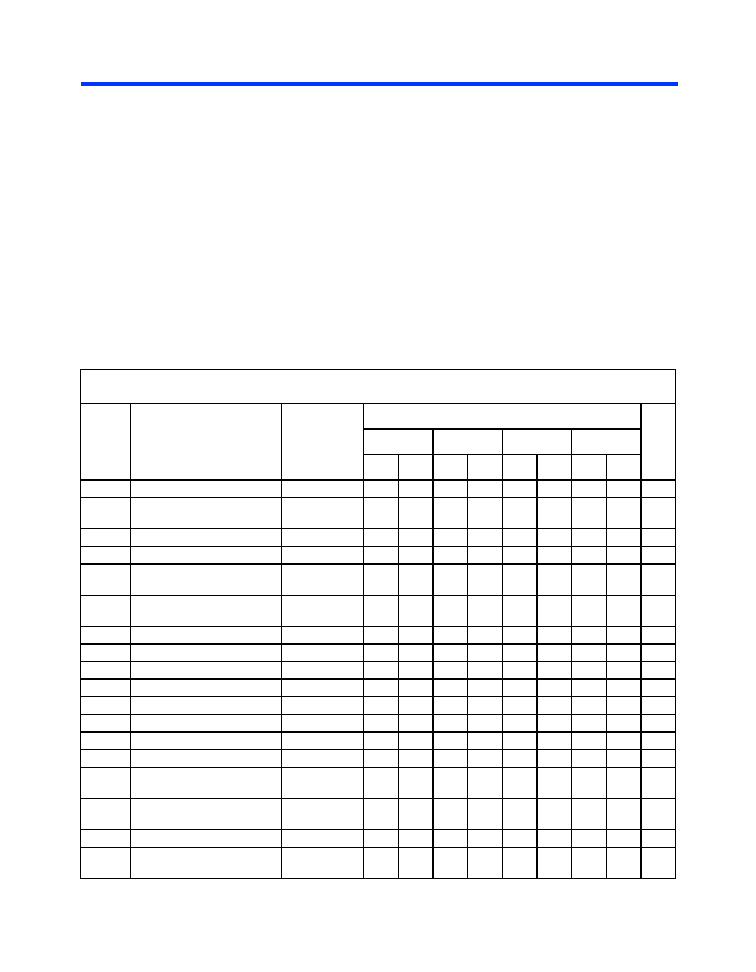

Table 33. EPM7160S External Timing Parameters (Part 1 of 2)

Symbol

Parameter

Conditions

Speed Grade

Unit

-6

-7

-10

-15

MinMax MinMax MinMax MinMax

tPD1

Input to non-registered output

C1 = 35 pF

6.0

7.5

10.0

15.0

ns

tPD2

I/O input to non-registered

output

C1 = 35 pF

6.0

7.5

10.0

15.0

ns

tSU

Global clock setup time

3.4

4.2

7.0

11.0

ns

tH

Global clock hold time

0.0

ns

tFSU

Global clock setup time of fast

input

2.5

3.0

ns

tFH

Global clock hold time of fast

input

0.0

0.5

0.0

ns

tCO1

Global clock to output delay

C1 = 35 pF

3.9

4.8

5

8

ns

tCH

Global clock high time

3.0

4.0

5.0

ns

tCL

Global clock low time

3.0

4.0

5.0

ns

tASU

Array clock setup time

0.9

1.1

2.0

4.0

ns

tAH

Array clock hold time

1.7

2.1

3.0

4.0

ns

tACO1

Array clock to output delay

C1 = 35 pF

6.4

7.9

10.0

15.0

ns

tACH

Array clock high time

3.0

4.0

6.0

ns

tACL

Array clock low time

3.0

4.0

6.0

ns

tCPPW

Minimum pulse width for clear

and preset

2.5

3.0

4.0

6.0

ns

tODH

Output data hold time after

clock

C1 = 35 pF (3)

1.0

ns

tCNT

Minimum global clock period

6.7

8.2

10.0

13.0

ns

fCNT

Maximum internal global clock

frequency

149.3

122.0

100.0

76.9

MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EPM570F100I5N | IC MAX II CPLD 570 LE 100-FBGA |

| THF476K035P1G-F | CAP TANT 47UF 35V 10% AXIAL |

| EPM3128ATC100-5N | IC MAX 3000A CPLD 128 100-TQFP |

| EPM3128ATC100-5 | IC MAX 3000A CPLD 128 100-TQFP |

| EPM570T100C4N | IC MAX II CPLD 570 LE 100-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPM7128SLC84-15 | 制造商:Altera Corporation 功能描述:MAX DEVICE |

| EPM7128SLC84-15N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 128 Macro 68 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7128SLC84-15N | 制造商:Altera Corporation 功能描述:PROGRAMMABLE LOGIC IC |

| EPM7128SLC84-6 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 128 Macro 68 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7128SLC846F | 制造商:ALTERA 功能描述:* |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。