- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄15530 > EVAL-ADUC7023QSPZ1 (Analog Devices Inc)BOARD EVAL FOR ADUC7023 PDF資料下載

參數(shù)資料

| 型號: | EVAL-ADUC7023QSPZ1 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 76/96頁 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADUC7023 |

| 標準包裝: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 類型: | MCU |

| 適用于相關產(chǎn)品: | ADuC7023 |

| 所含物品: | 板 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當前第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

ADuC7023

Data Sheet

| Page 78 of 96

FIQSTA

FIQSTA is a read-only register that provides the current enabled

FIQ source status (effectively a logic AND of the FIQSIG and

FIQEN bits). When set to 1, that source generates an active FIQ

request to the ARM7TDMI core. There is no priority encoder

or interrupt vector generation. This function is implemented in

software in a common interrupt handler routine.

FIQSTA Register

Name:

FIQSTA

Address:

0xFFFF0100

Default value: 0x00000000

Access:

Read only

Programmed Interrupts

Because the programmed interrupts are not maskable, they are

controlled by another register (SWICFG) that writes into both

IRQSTA and IRQSIG registers and/or the FIQSTA and FIQSIG

registers at the same time.

The 32-bit register dedicated to software interrupt is SWICFG

described in Table 89. This MMR allows the control of a

programmed source interrupt.

Table 89. SWICFG MMR Bit Designations

Bit

Description

31 to 3

Reserved.

2

Programmed interrupt FIQ. Setting/clearing this bit

corresponds to setting/clearing Bit 1 of FIQSTA and

FIQSIG.

1

Programmed interrupt IRQ. Setting/clearing this bit

corresponds to setting/clearing Bit 1 of IRQSTA and

IRQSIG.

0

Reserved.

Any interrupt signal must be active for at least the minimum

interrupt latency time, to be detected by the interrupt controller

and to be detected by the user in the IRQSTA and FIQSTA

registers.

08675-

035

POINTER TO

FUNCTION

(IRQVEC)

IRQ_SOURCE

FIQ_SOURCE

PROGRAMMABLE PRIORITY

PER INTERRUPT (IRQP0/IRQP1/IRQP2)

INTERNAL

ARBITER

LOGIC

INTERRUPT VECTOR

BIT 31 TO

BIT 23

UNUSED

BIT 1 TO

BIT 0

LBSs

BIT 22 TO BIT 7

(IRQBASE)

BIT 6 TO

BIT 2

HIGHEST

PRIORITY

ACTIVE IRQ

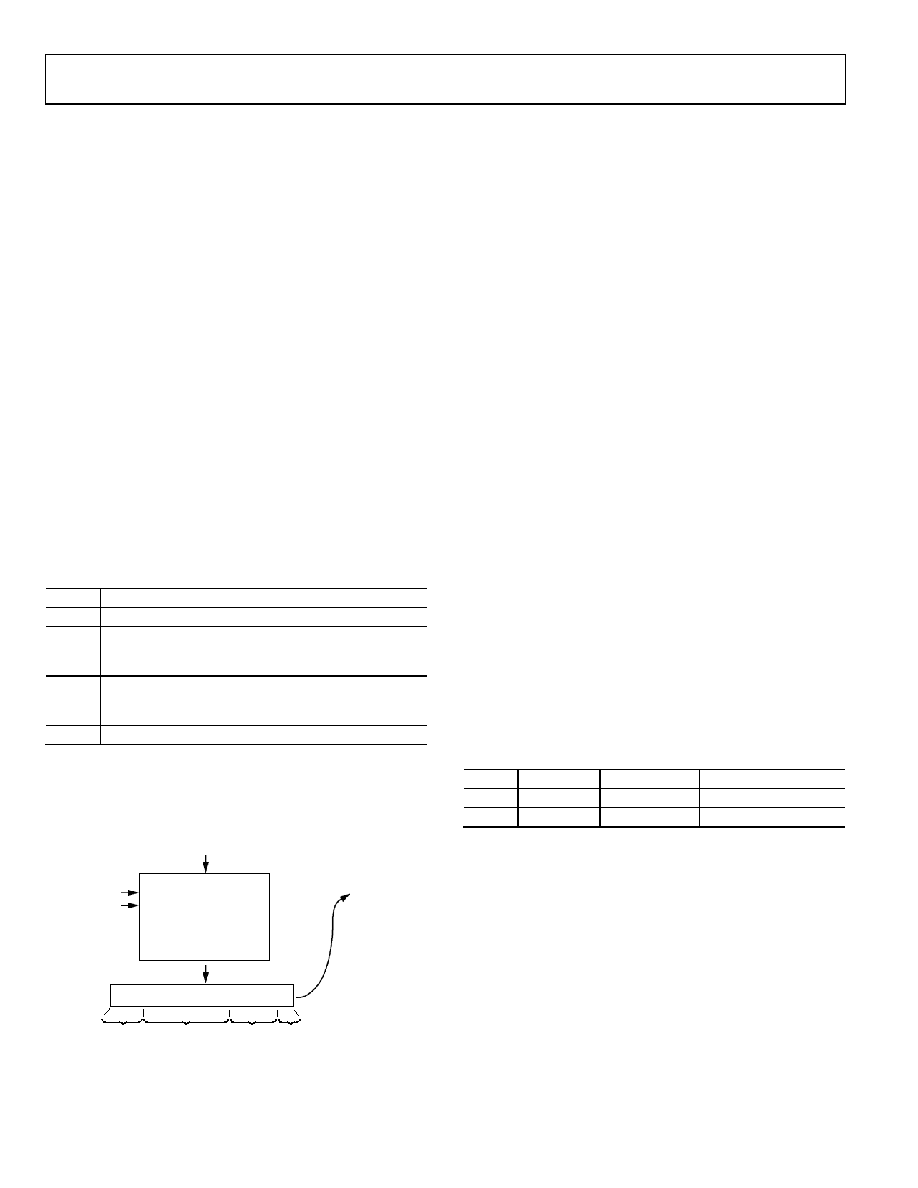

Figure 41. Interrupt Structure

VECTORED INTERRUPT CONTROLLER (VIC)

The ADuC7023 incorporates an enhanced interrupt control

system or vectored interrupt controller. The vectored interrupt

controller for IRQ interrupt sources is enabled by setting Bit 0

of the IRQCONN register. Similarly, Bit 1 of IRQCONN enables

the vectored interrupt controller for the FIQ interrupt sources.

The vectored interrupt controller provides the following

enhancements to the standard IRQ/FIQ interrupts:

Vectored interrupts allow a user to define separate interrupt

service routine addresses for every interrupt source. This is

achieved by using the IRQBASE and IRQVEC registers.

IRQ/FIQ interrupts can be nested up to eight levels depending

on the priority settings. An FIQ still has a higher priority

than an IRQ. Therefore, if the VIC is enabled for both the

FIQ and IRQ and prioritization is maximized, then it is

possible to have 16 separate interrupt levels.

Programmable interrupt priorities, using the IRQP0 to IRQP2

registers, can be assigned an interrupt priority level value

between 0 and 7.

VIC MMRs

IRQBASE Register

The vector base register, IRQBASE, is used to point to the start

address of memory used to store 32 pointer addresses. These

pointer addresses are the addresses of the individual interrupt

service routines.

Name:

IRQBASE

Address:

0xFFFF0014

Default value: 0x00000000

Access:

Read and write

Table 90. IRQBASE MMR Bit Designations

Bit

Type

Initial Value

Description

31:16

Read only

Reserved

Always read as 0.

15:0

R/W

0

Vector base address.

Rev. E

相關PDF資料 |

PDF描述 |

|---|---|

| AIUR-10-182K | INDUCTOR POWER 1800UH 10% T/H |

| EYM15DRSD | CONN EDGECARD 30POS DIP .156 SLD |

| V300C3V3C50B | CONVERTER MOD DC/DC 3.3V 50W |

| AIUR-06-271K | INDUCTOR POWER 270UH 10% T/H |

| EGM15DRSD | CONN EDGECARD 30POS DIP .156 SLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EVAL-ADuC7023QSPZ2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Precision Analog Microcontroller, 12-Bit Analog I/O, ARM7TDMI MCU with Enhanced IRQ Handler |

| EVALADUC7023QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVAL-ADUC7024QS | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Bulk |

| EVAL-ADUC7024QS-U2 | 制造商:Analog Devices 功能描述:QUICK START DEVL SYST EVAL BOARD I.C. - Bulk |

| EVAL-ADUC7024QS-U3 | 制造商:Analog Devices 功能描述:ARM7 ADUC7024 QUICKSTART DEV KIT |

發(fā)布緊急采購,3分鐘左右您將得到回復。